AMDが次世代EPYCプロセッサ「Venice」をTSMCの最先端2nm(N2)プロセス技術で製造することを正式に発表した。Zen 6アーキテクチャを採用する同プロセッサは、業界初のHPC(ハイパフォーマンスコンピューティング)向け2nmプロダクトとなり、2026年の発売を予定している。

AMDのZen 6ベース「Venice」、TSMCの2nmプロセスで業界初のテープアウトに成功

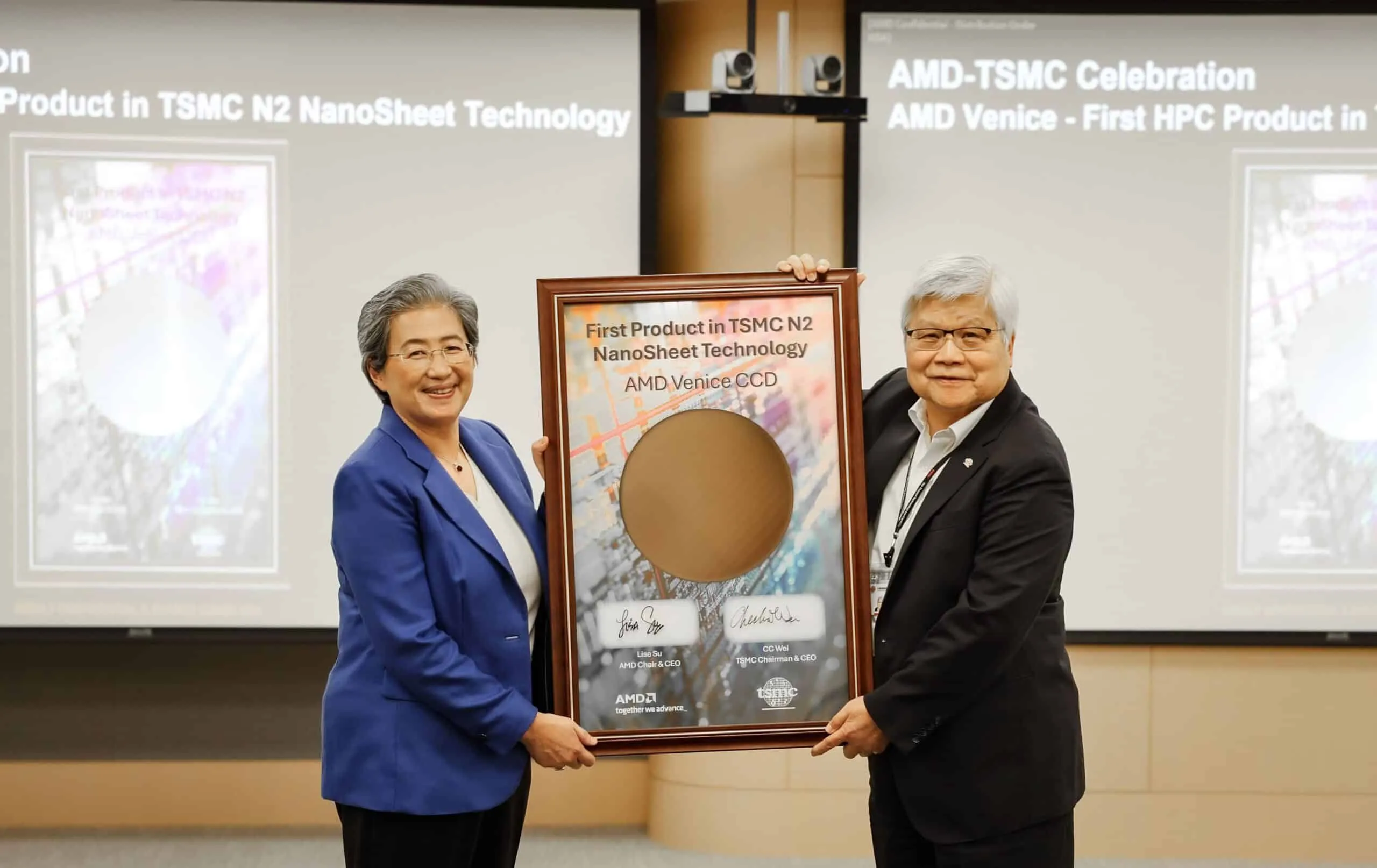

AMDは2025年4月14日(米国時間)、次世代EPYCプロセッサ「Venice」がTSMCの最先端2nm(N2)プロセス技術において、業界初のHPC製品としてテープアウトと初期動作確認に成功したことを発表した。テープアウトとは、半導体設計が完了し製造準備が整ったことを示す重要なマイルストーンだ。この段階を経ることで、実際のシリコンチップとして製造される道が開かれる。

この発表は、AMDとTSMCの半導体製造パートナーシップの強さを示すとともに、AMDのデータセンターCPUロードマップにおける大きな進展を意味している。Zen 6アーキテクチャを採用する「Venice」プロセッサは計画通り来年の発売を目指している。

「TSMCは長年にわたる重要なパートナーであり、彼らのR&D・製造チームとの深い協力関係により、AMDは高性能コンピューティングの限界を押し広げるリーダーシップ製品を一貫して提供することができています。TSMCのN2プロセスおよびアリゾナFab 21の主要HPCカスタマーであることは、私たちがコンピューティングの未来を支える革新と先進技術の提供に向けて密接に協力している素晴らしい例です」とAMD会長兼CEOのLisa Su博士は述べている。

Zen 6アーキテクチャとTSMC 2nmプロセスの技術詳細

「Venice」と呼ばれる次世代EPYCプロセッサは、AMDの最新設計となる「Zen 6」アーキテクチャを採用している。これは現行の「Zen 5」アーキテクチャからさらに進化したもので、性能と電力効率の大幅な向上が期待されている。

TSMCの2nmプロセス(N2)は、同社の最先端製造技術であり、革新的なNanoSheet技術を採用している。従来のFinFET構造から進化したNanoSheet技術は、トランジスタの三次元構造をさらに最適化することで、より高い集積度と電力効率を実現する。この技術により、チップ面積あたりのトランジスタ数の増加、消費電力の削減、処理性能の向上が可能になる。

AMDのZen 6アーキテクチャはこのTSMC 2nmプロセスと共同最適化されることで、最大限のパフォーマンスを発揮する設計となっている。この「アーキテクチャと製造プロセスの共同最適化」は、先端半導体開発の鍵となる戦略であり、AMDとTSMCの緊密な協力関係がそれを可能にしている。

「AMDが当社の先進的な2nm(N2)プロセス技術とTSMCアリゾナ工場の主要HPCカスタマーであることを誇りに思います。協力して重要な技術スケーリングを進めることにより、高性能シリコンのパフォーマンス、電力効率、歩留まりの向上を実現しています」とTSMC会長兼CEOのC.C. Wei博士は述べている。

半導体製造の国内回帰:TSMCアリゾナ工場での第5世代EPYC検証の意義

AMDはまた、第5世代EPYC CPUがTSMCのアリゾナ新工場(Fab 21)で正常に動作することの検証にも成功したと発表した。これは米国における最先端半導体製造の重要なマイルストーンであり、近年加速している半導体製造の国内回帰戦略の成功を示すものである。

米国は国家安全保障と技術主導権の観点から、CHIPSおよび科学法などの政策を通じて最新半導体の国内製造能力の強化を積極的に推進している。グローバルサプライチェーンの脆弱性が明らかになった近年、半導体の供給安全保障は各国の重要課題となっている。

TSMCアリゾナ工場での検証成功は、単なる製造地の移転ではなく、最先端技術の米国内での実現という点で大きな意義を持つ。これにより、米国内での高度な技術開発サイクルが確立され、イノベーションの加速が期待される。

Zen 6搭載2nmプロセスの意義と業界への影響

AMDのZen 6アーキテクチャを採用した2nmプロセスのEPYCプロセッサは、データセンターやハイパフォーマンスコンピューティング市場に大きな影響を与えると予想される。特に電力効率の向上は、大規模データセンターの運用コスト削減とカーボンフットプリント軽減に直結する重要な要素だ。

半導体製造プロセスの微細化は、ムーアの法則として知られる半導体の指数関数的進化の基盤となってきた。2nmへの移行は、この法則を維持する次なる一歩であり、計算能力のさらなる向上を可能にする。これはAI、機械学習、科学計算などの計算集約型アプリケーションの発展にとって不可欠である。

TSMCの2nmプロセス技術の実用化は、半導体業界全体の技術革新を加速させる触媒となる可能性がある。AMDがリードカスタマーとして先陣を切ることで、他の半導体設計企業も追随する形で最先端プロセスの採用が進むと見られている。

AMDの競争戦略とZen 6ベース2nmプロセッサの位置づけ

今回の発表は、AMDのサーバーCPU市場におけるシェア拡大戦略の一環としても重要な意味を持つ。現在Intelが主導するサーバープロセッサ市場において、AMDはZen 6ベースの次世代EPYCプロセッサで技術的優位性をさらに高める狙いがある。

Zen 6アーキテクチャを2nmプロセスで製造することにより、AMDは性能向上と電力効率の両面でのリーダーシップを目指している。この戦略は、特に電力コストが大きな課題となるハイパースケールデータセンター事業者にとって魅力的な選択肢となるだろう。

また、AIワークロードやHPC(高性能計算)など、計算処理能力と電力効率の両方が求められる領域においても、Zen 6ベースの2nmプロセスEPYCプロセッサは競争力を発揮すると期待されている。

さらに、AMDが構築してきたチップレット設計アプローチと2nmプロセス技術の組み合わせは、スケーラビリティとコスト効率の両面でも優位性をもたらす可能性がある。これにより、様々な規模と要件を持つデータセンター市場においてAMDの選択肢が広がると見られている。

Source