1960年代から半世紀以上にわたり、人類の計算能力はシリコンという単一の元素によって牽引されてきた。2年ごとにトランジスタの実装密度が倍増するという「ムーアの法則」は、部屋を占拠するほどの巨大なメインフレームを、我々のポケットに収まるスマートフォンへと変貌させた。そして現在、人工知能(AI)や大規模言語モデル(LLM)の爆発的な普及は、かつてない桁違いの計算能力を世界中のデータセンターに要求している。

しかし、その栄華を極めたシリコンの支配が終わりを迎えようとしている。トランジスタの微細化が限界点に達し、物理法則そのものが立ちはだかっているのだ。この限界を突破する切り札として長年期待されてきたのが、原子数個分の薄さしか持たない「2次元(2D)半導体」である。長らく製造速度の遅さと特性の偏りという致命的な欠点に縛られてきたこの新素材に対し、中国の研究チームが全く新しいアプローチを提示した。彼らは「液体金 (Liquid Gold)」を用いた独自の化学気相成長(CVD)法を開発し、新素材である単層タングステンシリコン窒化物を従来の約1,000倍という驚異的な速度で成長させることに成功したのだ。

シリコン王国の過密都市と、電子たちが引き起こす量子空間の反乱

現代のマイクロチップは、何十億ものトランジスタが規則正しく並ぶ極小の超巨大都市である。トランジスタは電流のオン・オフを切り替えるスイッチであり、これを小型化すればするほど、一定面積内に詰め込めるスイッチの数が増え、計算能力が向上する。

だが、この都市開発は物理的な限界に直面している。電流の通り道であるチャネルの長さが10ナノメートルを下回ると、都市は異常な過密状態に陥る。半導体業界はこれまで、立体的なヒレ状の構造を持つFinFETや、ゲートがチャネルを完全に囲い込むGate-All-Around(GAA)構造などを考案し、微細化の延命を図ってきた。しかし、5ナノメートルという極小の領域(サブ5nmノード)に突入すると、電子は古典力学の粒子としての振る舞いを捨て、確率の波として空間に広がる性質を見せ始める。「量子トンネル効果」と呼ばれる現象である。

本来であれば電流を遮断すべき絶縁の壁を、電子がまるで幽霊のようにすり抜けてしまうのだ。スイッチを切っているはずなのに電流が漏れ出し(リーク電流)、それが膨大な無駄な熱を生み出す。この「電力の壁」と「短チャネル効果」は、シリコンをベースにしたアーキテクチャの性能向上を根本から阻害している。

業界はこれまでも、カーボンナノチューブやシリコンカーバイド(SiC)、窒化ガリウム(GaN)など、シリコンの代替となる物質を模索してきた。しかし、カーボンナノチューブは何十億個ものチューブを均一な方向へ配置することが極めて難しく、SiCやGaNは高電圧に耐えるパワー半導体には向いているものの、超高密度の論理回路(IC)には不適である。そこで最有力候補として浮上したのが、物質を極限まで薄く切り出した「2次元半導体」である。物質が原子1個から数個分の薄さになると、「量子閉じ込め効果」が働き、電子の移動範囲が2次元の平面に厳密に制限される。これは物理学の「箱の中の粒子」モデルに似ており、粒子を狭い空間に閉じ込めることで最低エネルギー状態が上昇し、物質のバンドギャップ(電子が超えなければならないエネルギーの谷)が広がる。結果として、オフ状態のスイッチが完全に電流を遮断し、漏れ電流を劇的に抑え込むことが可能になる。

2次元空間のジレンマ。絶望的な遅延と「p型の枯渇」

理論上の美しさとは裏腹に、2次元半導体を産業レベルで製造する試みは長らく暗礁に乗り上げていた。そこに立ちはだかるのは、圧倒的な製造スピードの遅さと、論理回路を構築するための材料の偏りという2つのアポリアである。

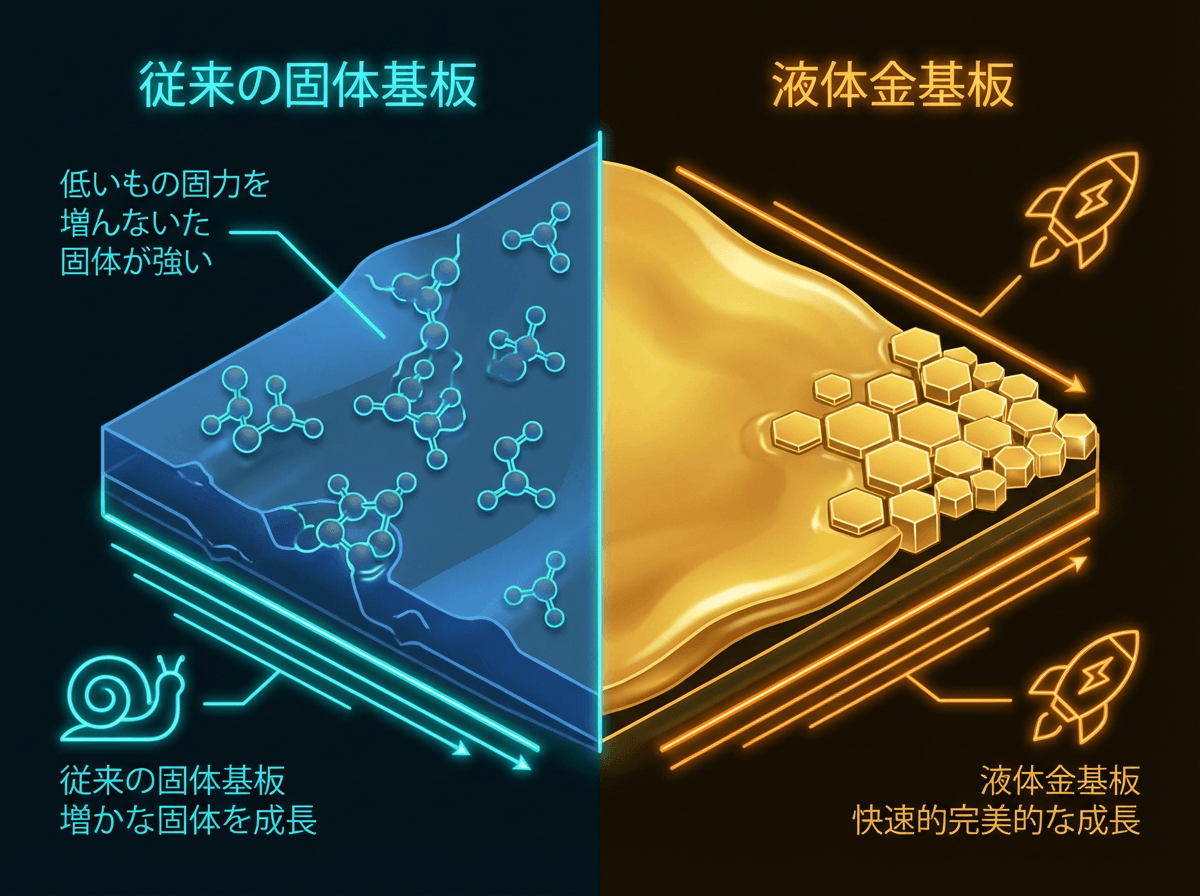

通常、これらの材料は化学気相成長(CVD)という手法で作られる。加熱した基板の上にガス状の前駆体を流し込み、基板表面で化学反応を起こして原子を一つずつ定着させていくプロセスである。従来の固体基板を用いたCVD法では、材料の成長速度は絶望的に遅かった。前駆体ガスの拡散速度や、固体表面での核生成の遅さが足を引っ張り、典型的な成長速度は5時間で約1マイクロメートル(0.00004インチ)にとどまる。これを現代の製造プロセスで主流となっている直径300ミリメートルの商用ウェーハに適用することは、物理的な時間を考慮すると全く現実味がない。

さらに設計上の致命傷となるのが「p型」材料の欠如である。現代の論理回路(CMOS)は、電子が主役となってマイナスの電荷を運ぶ「n型」半導体と、電子の抜け穴(正孔=ホール)がプラスの電荷のように振る舞って移動する「p型」半導体のペアで構成されている。グラフェンにはそもそもバンドギャップがなく、トランジスタのスイッチに使えない。二硫化モリブデン(MoS₂)や二セレン化モリブデン(MoSe₂)といった遷移金属ダイカルコゲナイドの多くはn型である。高い性能と安定性を兼ね備えたp型の2次元材料を見つけ出し、さらにその特性を意図的に制御(ドーピング)することは、世界の半導体研究において最も激しく争われる最前線となっていた。

液体金のスケートリンクが描く1000倍速の結晶ネットワーク

中国の国防科技大学のZhu Mengjian、および中国科学院金属研究所のRen Wencai、Xu Chuanらが率いる研究チームは、この膠着状態を打ち破る手法を学術誌『National Science Review』に発表した。彼らが採用したのは、「液体金とタングステンの二層(Au/W bilayer)」を成長基板として用いるというアプローチである。

従来の固体基板には目に見えない凹凸や結晶の境目(粒界)が存在し、これが原子の移動を阻害して成長を遅らせていた。研究チームは基板の表面を液体の金で覆うことで、この障壁を完全に消し去った。液体の表面には一切の粒界が存在しない。それは前駆体の原子にとって、摩擦を全く感じさせない滑らかな「スケートリンク」を意味する。

ここでの化学的プロセスは極めて精緻である。まず、液体の金表面は前駆体原子の表面拡散を劇的に加速させる。原子はこのリンクの上を高速で滑りながら互いに結びつき、瞬く間に規則正しい単結晶のネットワークを組み上げていく。同時に、下層に配置された固体のタングステン層が、フィルムの構成要素となるタングステン原子を直接供給しつつ、触媒的な役割を果たす。従来のCVDがすべてガスからの原子供給に依存していたのに対し、基板自体が素材の供給源となることで、反応速度の律速段階が解消されたのである。

このプロセスの最適化により、単層の「タングステンシリコン窒化物(WSi₂N₄)」フィルムの成長速度は、1分あたり約20マイクロメートル(0.0008インチ)に達した。従来手法の5時間で1マイクロメートルという速度と比較すると、約1,000倍の加速である。生成されたフィルムの最終サイズは3.6cm × 1.8cmに達し、内部の単結晶ドメインはサブミリメートル規模にまで拡大された。

パズルの完成。p型タングステンシリコン窒化物がもたらす熱と速度の革新

この手法によって高速生成されたタングステンシリコン窒化物(WSi₂N₄)の真の価値は、ドーピングの調整によって安定したp型の挙動を示す点にある。

長らく空席だったp型のピースが埋まることで、n型のMoS₂などと組み合わせた完全な2D-CMOS論理回路の構築が視野に入る。この新素材はトランジスタの性能指標において、極めて高い正孔移動度(ホールモビリティ)と高いオン状態電流密度を記録した。正孔移動度が高いということは、電子の「空席」が結晶内を高速で移動できることを意味し、スイッチの開閉速度、ひいてはプロセッサのクロック周波数向上に直結する。

| 比較項目 | 従来のCVD法(例:MoS₂など) | 本研究の新手法(WSi₂N₄) | シリコン(現行のバルク材料) |

|---|---|---|---|

| 主たる電荷キャリア | 電子(n型偏重) | 正孔(p型)の制御・調整が可能 | n型/p型の双方が確立済み |

| 成長・加工基板 | 固体基板(サファイア等) | 液体金 / タングステン二層 | 単結晶シリコンインゴット |

| 成長速度の目安 | 5時間で約1マイクロメートル | 1分間で約20マイクロメートル | 確立された大規模工業プロセス |

| 量子トンネル耐性 | 非常に高い(2D構造による) | 非常に高い(2D構造による) | サブ5nm領域で著しく低下 |

| 熱管理特性 | 熱伝導率が低く熱が滞留しやすい | 高い機械的強度と優れた熱伝導性 | 冷却構造の微細化が限界 |

極薄の2D材料が常に抱える「熱だまり」の問題に対しても、WSi₂N₄は優れた熱伝導性を示すことで応えている。強い機械的強度と高い化学的安定性も併せ持っており、リソグラフィやエッチングといった過酷な半導体製造プロセスに耐えうる耐久性を備えている。液中環境下でのセンサーや、生体と接合するバイオ電子デバイスへの応用も想定されるほどの物理的靭性を持つ。

EUVの壁を迂回せよ。米中半導体戦争とゲームチェンジャーの地政学

このブレイクスルーを単一の材料科学の進歩として片付けることはできない。現在のグローバルな半導体産業の構造と、地政学的なパワーバランスの観点から見ると、全く異なる風景が浮かび上がる。

現在、先端半導体の微細化を牽引しているのは、オランダのASMLが独占的に製造する極端紫外線(EUV)露光装置である。TSMCやインテル、サムスン電子といった巨大ファウンドリは、このEUV技術を用いてシリコンの微細化を推し進め、高NA(開口数)EUVと呼ばれる次世代装置を用いたロードマップを描いている。対照的に、米国による厳格な輸出規制(エンティティ・リスト等)により、中国の半導体メーカーはこれらの最新鋭装置を入手できない。既存のシリコンの微細化競争において、中国は構造的に不利な立場に置かれている。

中国が既存のシリコンベースの微細化ルートを迂回し、新素材によるアーキテクチャの刷新に莫大なリソースを注ぎ込んでいる理由はここにある。シリコンを極限まで削り出すのではなく、最初から原子レベルの薄さを持つ2D材料を高効率で量産できれば、ASMLのEUV露光装置に依存しない新しいチップ製造のパラダイムを構築できる可能性がある。液体金を用いた高速CVD技術は、西側諸国が築き上げたシリコンとEUVの強固な城壁を飛び越えるための、国家戦略に基づく生存のベクトルである。

研究の空白地帯。実験室の魔法を巨大工場へ移植する闘い

ポスト・ムーア時代の半導体技術において、一つの強力なマイルストーンが打ち立てられたことは間違いない。しかし、この成果が直ちに明日のスマートフォンやAIサーバーに搭載されるわけではない。

実験室で生成された3.6cm × 1.8cmのフィルムから、現代の半導体工場の標準である300ミリメートルウェーハでの量産化へのスケールアップには、未だ解明されていない工学の課題が山積している。液体金属を用いた特殊な二層基板を、数千枚単位で連続処理するウェーハ製造ラインにどう適応させるのか。面積が広がれば広がるほど、原子レベルの均一性を維持し、数十億のトランジスタが完璧に動作するための欠陥密度の低減は指数関数的に困難になる。

加えて、デバイスインテグレーション特有の課題も残されている。2D材料と外部の金属配線を繋ぐ部分で発生する高いコンタクト抵抗は、依然として業界全体の悩みの種である。新しい材料を既存のCMOS製造ラインに組み込むためには、材料そのものの研究だけでなく、エッチングの化学薬品や配線プロセスを根本から再設計する必要がある。

液体金属基板と高速成長技術の組み合わせは、半導体の歴史における新たな地平を開いた。無数の電子がシリコンの立体迷路を限界まで駆け抜けた時代が終わり、原子数個分の極薄の平面を高速で滑空する新たな時代が幕を開けようとしている。西側の微細化ロードマップと東側の新素材アプローチが交錯する中で、次世代計算機の覇権を懸けた開発競争は、より苛烈なステージへと突入する。

Sources

- South China Morning Post: Semiconductor leap: China looks to next-gen ‘2D chip’ with 1,000-fold growth speed