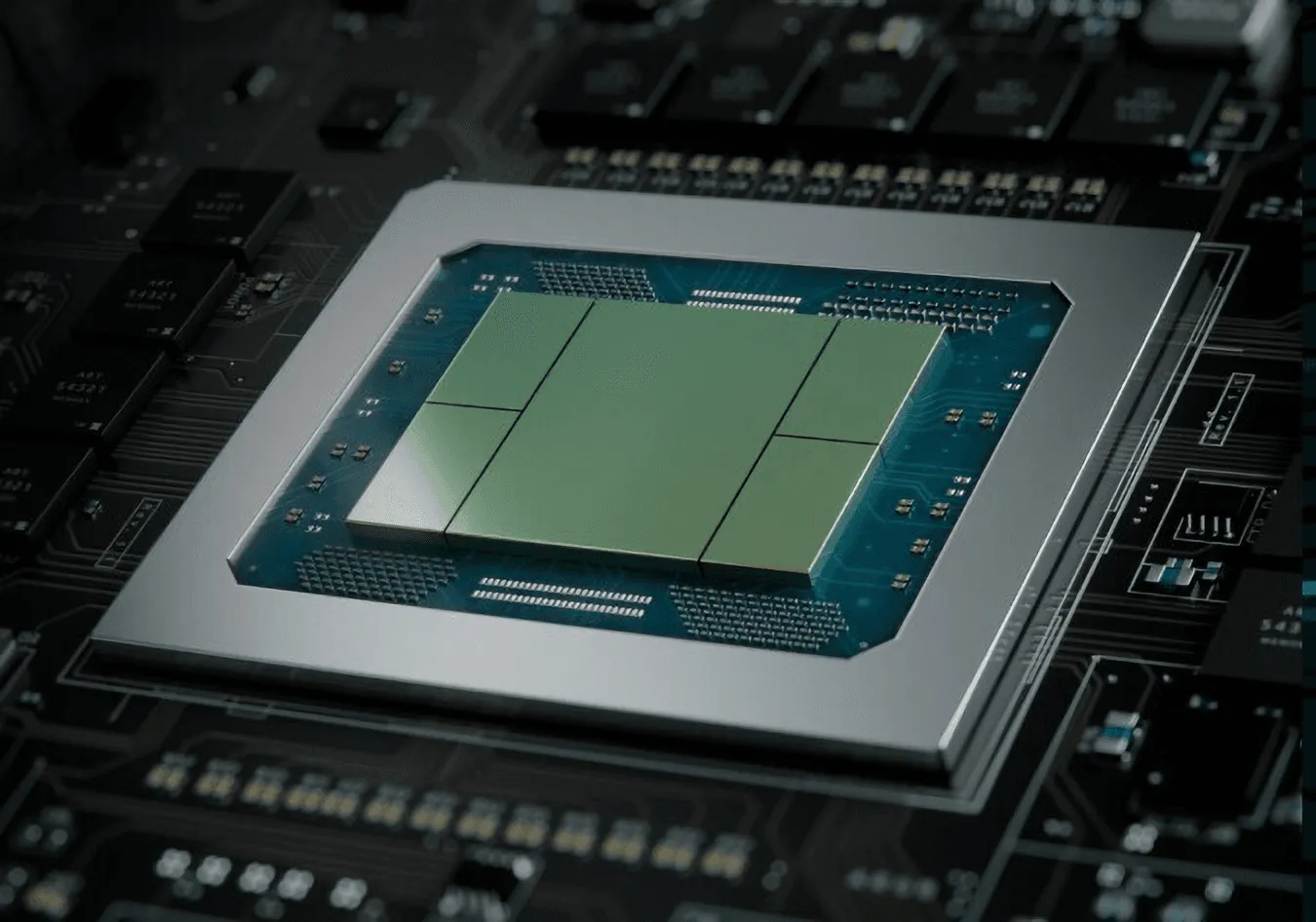

半導体の微細化競争が物理的な限界に近づく中、業界は「ムーアの法則の次」を模索している。そんな中、Marvell Technologyが、業界初となる2nmプロセスを採用したカスタムSRAM(Static Random Access Memory)の開発を発表した。これはAIデータセンターの性能、電力効率、そして経済性を根本から覆し、AIチップ開発のゲームのルールそのものを変えうる、象徴的な一歩と捉えるべきかも知れない。

Marvellが投じた2nmカスタムSRAMという一石

Marvellが2025年6月17日(現地時間)に発表したカスタムSRAMは、AIの頭脳となるカスタムXPU(eXtreme Processing Unit)や各種デバイスの性能を飛躍的に高めることを目的として設計されている。まずは、その驚くべきスペックから見ていこう。

- メモリ容量と速度: 最大6ギガビットの高速メモリを、最大3.75GHzという高クロックで動作させる。

- 面積効率の革命: 業界最高の「平方ミリメートルあたりの帯域幅」を実現し、チップ全体のダイ(半導体本体)面積を最大15%も削減可能にする。

- 驚異的な省電力性: 同等密度の標準的なオンチップSRAMと比較して、待機電力を最大66%も削減する。

これらの数字が持つ意味は、極めて大きい。「ダイ面積15%削減」は、チップ設計者にとって、限られたシリコンという「土地」に新たな可能性を拓くものに他ならない。空いたスペースには、より多くの演算コアを詰め込んだり、さらに大容量のキャッシュメモリを搭載したり、あるいはチップ自体のサイズを縮小してコストを下げることもできる。アプリケーションの特性やTCO(総所有コスト)目標に応じて、最適な設計を追求する自由度が一気に高まるのだ。

また、「待機電力66%削減」は、特に大規模なAIクラスタやデータセンターにおいて、死活問題となりつつある消費電力と熱問題を緩和する上で絶大な効果を発揮する。AIの性能向上は、しばしば電力消費の爆発的な増加と表裏一体であったが、Marvellのアプローチは、このトレードオフの関係に風穴を開ける可能性を示唆している。

なぜ今「カスタムSRAM」が重要なのか?― AIとムーアの法則の限界

この発表の真の重要性を理解するためには、現在の半導体業界が直面する二つの大きな課題に目を向ける必要がある。それは「AIが引き起こすメモリの壁」と「ムーアの法則の終焉」だ。

AIが直面する「メモリの壁」問題

現代のAIモデル、特に大規模言語モデル(LLM)などは、膨大なパラメータを処理するために、かつてないほど広大なメモリ帯域と容量を要求する。しかし、プロセッサの演算性能の向上ペースに、メモリのデータ転送速度が追いつかない「メモリの壁」または「フォン・ノイマン・ボトルネック」と呼ばれる問題が深刻化している。いくら強力なエンジン(プロセッサ)を積んでも、燃料(データ)を十分に供給できなければ、その性能をフルに発揮することはできない。

この課題を解決するためには、プロセッサのできるだけ近くに、高速かつ大容量のメモリを配置する必要がある。CPU内部に搭載されるSRAMは、最も高速なメモリだが、その集積度とコストには限界があった。MarvellのカスタムSRAMは、このSRAMの性能と効率を極限まで高めることで、メモリの壁を打ち破るための強力な武器となる。

汎用から専用へ:カスタムシリコン時代の到来

かつて半導体業界は、「ムーアの法則」に従い、トランジスタを微細化することで性能と電力効率を向上させてきた。しかし、2nmという最先端プロセスにまで到達した現在、微細化のコストと技術的困難は増大の一途をたどっている。

この状況を打開する鍵として注目されているのが「カスタムシリコン」だ。特定のワークロード(例えばAI推論や学習)に特化してチップを設計することで、汎用チップでは達成不可能なレベルの性能と効率を引き出すアプローチである。GoogleのTPU、AmazonのTrainium/Inferentia、MicrosoftのMaiaなどは、この潮流を代表する存在だ。

Marvellの発表は、こうしたハイパースケーラーやその他の企業が独自のカスタムチップを開発する上で、不可欠な「部品」を提供するという戦略に基づいている。Will Chu氏(Marvell, Custom Cloud Solutions担当シニアバイスプレジデント)が「カスタムはAIインフラの未来だ」と語るように、同社はこのカスタムシリコン時代において、設計者を支える重要なプラットフォーマーとしての地位を確立しようとしているのだ。

点から線へ:Marvellが描く包括的なメモリ戦略の全貌

今回の2nmカスタムSRAMは、Marvellの壮大な戦略における、ジグソーパズルの重要なピースの一つに過ぎない。同社はこれまでにも、AIインフラのメモリ階層をあらゆる角度から最適化するための技術を次々と発表してきた。

- CXL (Compute Express Link) 技術: サーバー内のメモリ容量をテラバイト級に拡張し、リソースの柔軟な共有を可能にする。

- カスタムHBM (High-Bandwidth Memory) 技術: プロセッサパッケージ内に積層される広帯域メモリの容量を最大33%増加させつつ、スペースと電力を削減する。

そして今回、プロセッサの最も内側、つまりオンダイに搭載される「カスタムSRAM」が加わった。これにより、Marvellは「オンダイ(SRAM)」「パッケージ内(HBM)」「システムレベル(CXL)」という、メモリ階層のすべてをカバーする包括的なソリューションポートフォリオを完成させたことになる。

市場調査会社650 Groupの共同創業者であるAlan Weckel氏が「Marvellの、あらゆる接点でメモリ性能を改善しようとする包括的なアプローチは説得力がある」と評価するように、この多層的な戦略こそがMarvellの最大の強みと言えるだろう。それぞれの技術が個別に機能するだけでなく、相互に連携することで、AIインフラ全体のパフォーマンスと効率を劇的に向上させる。これは、単一の技術だけでは達成できない、システムレベルでの最適化思想の現れだ。

Marvellが狙う「カスタム時代」のエコシステム戦略

Marvellの発表は、単なる高性能メモリコンポーネントのリリースではない。それは、ムーアの法則後の世界で半導体業界がどのように進化していくかを示す、一つの明確なロードマップだ。

同社は、SerDes(シリアライザ/デシリアライザ)、Die-to-dieインターコネクト、シリコンフォトニクス、PCIe Gen 7といった最先端のIP(知的財産)を幅広く保有している。これらを「部品」として提供し、顧客が独自のカスタムチップを効率的に開発できるプラットフォームを構築すること。それがMarvellの狙いである。いわば、半導体設計における「レゴブロック」の提供者となり、カスタムシリコンのエコシステムの中心に座ろうという野心的な戦略だ。

今回の2nmカスタムSRAMは、その戦略を加速させる強力なエンジンとなる。AIの進化が止まらない限り、メモリへの渇望が尽きることはない。その根源的な要求に応えることで、MarvellはAIインフラの進化を根底から支え、自らの存在価値を高めていくだろう。

Sources