現代の人工知能アルゴリズム、とりわけ大規模言語モデル(LLM)の学習および推論プロセスにおいて、計算能力の向上に対しデータ転送速度が追いつかない「メモリの壁」が深刻なボトルネックとなっている。GPTやGeminiに代表される膨大なパラメータを持つモデルでは、推論時のKVキャッシュの保持やトークン生成プロセスにおいて、極めて広帯域かつ大容量のメモリが絶え間なく要求される。この課題に対する現在の業界標準の最適解は、High Bandwidth Memory(HBM)である。しかし、HBMの構造は複雑を極める。完成した2D DRAMダイをシリコン貫通電極(TSV)を用いて物理的に積層し、微細なマイクロバンプを介してシリコンインターポーザ上でGPUやAIアクセラレータと近接実装するという、2.5Dあるいは3Dの極めて難易度の高いパッケージング技術を要求する。この多層積層と微細な接合プロセスは、熱放散の問題を引き起こし、さらに製造コストの著しい高騰と歩留まりの低下を招き、最先端AIハードウェアの供給制約の主要な要因となっている。

同時に、DRAMアーキテクチャ自体も深刻な物理的限界に直面している。従来の2D DRAMは、微細化を進めるにつれてキャパシタの物理的な体積が縮小し、データの最小単位である電荷の保持能力を維持することが困難になっている。平面方向へのスケーリングは限界点に到達しつつあり、これ以上の微細化は漏れ電流の増大やエラー率の上昇といった副作用を伴う。プロセッサの進化にメモリ容量と帯域幅の拡張が今後も追従するためには、かつてNANDフラッシュメモリが平面的微細化から立体的積層へと舵を切ったように、DRAMにおいても抜本的なアーキテクチャの転換が避けられない状況にある。

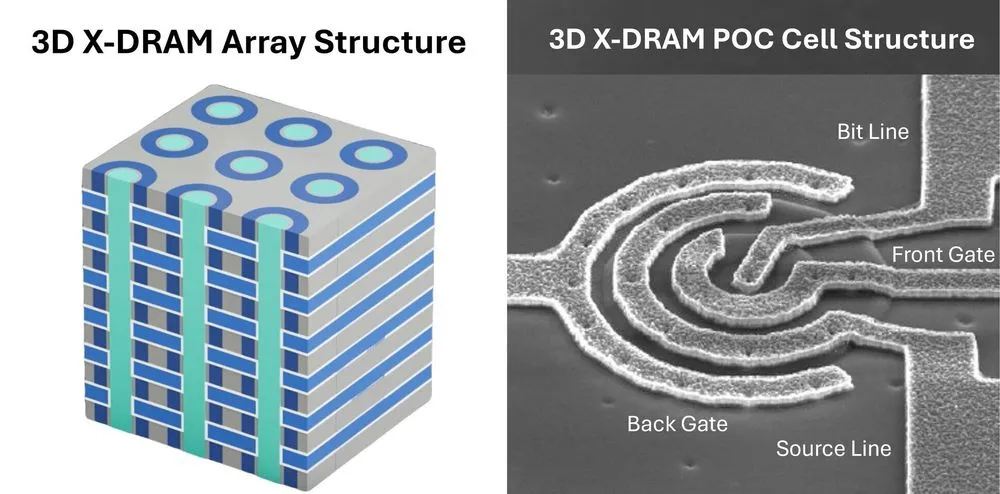

3D X-DRAMの概念実証が示す新たなパラダイム

こうした構造的課題に対し、シリコンバレーに拠点を置く次世代メモリ企業であるNEO Semiconductorは2026年4月23日、新技術である「3D X-DRAM」の概念実証(Proof-of-Concept: POC)に成功したことを発表した。この成果は、これまで理論上の設計図にとどまっていた次世代アーキテクチャが、実際のシリコン上で極めて高い要件を満たして稼働したことを意味し、メモリ業界における重大な技術的転換点となる。

この概念実証プロセスは、台湾の国立陽明交通大学(NYCU)に新設された産学イノベーション学院(IAIS)、および国家実験研究院の台湾半導体研究センター(NIAR-TSRI)との緊密な共同研究の下で実施された。提供されたPOCテストチップは、広範な電気的特性評価と長期的な信頼性試験を通過し、提案されている立体メモリアーキテクチャの堅牢性が確認されている。NEO Semiconductorの創業者兼CEOであるAndy Hsuは、この技術がAI時代に求められる高密度化と低コスト化を実現し、エネルギー効率を抜本的に改善する新しいスケーリング経路であると明言している。

技術的深層:3D NANDプロセスを転用するモノリシック積層の優位性

3D X-DRAMの最大の技術的特異点であり、ビジネスとしての実現可能性を高めている要素は、既存の3D NANDフラッシュメモリの製造インフラストラクチャを流用し、確立された製造設備と安定したプロセスを用いて製造可能であるという点にある。

HBMが「個別に製造された複数のDRAMダイをパッケージング段階で外部的に積み重ねる」アプローチであるのに対し、3D X-DRAMは「単一のシリコンダイの製造工程内部で、メモリセルを垂直方向に直接構築していく」モノリシックな立体構造を採用している。これは、すでに300層を超える積層技術が確立され、世界中のファブで日々大量生産されている3D NANDの製造プロセスに変更を最小限にとどめつつ適用できることを意味する。結果として、極めて高価なEUV(極端紫外線)露光装置への過度な依存を下げ、微細化によるキャパシタの物理的制約を回避しながら、層数を単純に増やすことで容量を飛躍的に拡張することが可能となる。同社の試算では、512Gbクラスのモジュールにおいて、従来の2D DRAMと比較して約10倍の記録密度を実現するという驚異的なスケーリングを描いている。

![FireShot Capture 045 - 3d X-DRAM - Neo Semiconductor - X-Nand - [neosemic.com].webp](https://media.xenospectrum.com/Fire_Shot_Capture_045_3d_X_DRAM_Neo_Semiconductor_X_Nand_neosemic_com_fb13667290.webp)

さらに、NEO Semiconductorはアーキテクチャの用途に応じた高度なセル構造を設計に組み込んでいる。大容量メモリが求められる用途向けには、メインストリームのDRAMやHBMロードマップと互換性を持つ1T1C(1トランジスタ・1キャパシタ)構造を用意した。一方、AIワークロードやインメモリコンピューティング(データが保存されている場所で直接計算を行う技術)向けには、電流検知動作に最適化されたキャパシタレスの3T0C(3トランジスタ・0キャパシタ)構造などを提案している。これらはIGZO(インジウム・ガリウム・亜鉛・酸化物)などの酸化物半導体チャネル技術を活用することで、トランジスタのオフ状態における漏れ電流を極限まで抑制する設計となっている。

特筆すべきは、この1T1Cや3T0Cに加え、浮遊体セル構造を利用した1T0Cのバリエーションも想定されていることである。これらの構造上の柔軟性により、単純なデータストレージ用途にとどまらず、プロセッサとメモリが同一のシリコン上でハイブリッドに統合される将来のロジックアーキテクチャにも対応しうる道筋が開かれている。このような微細構造の進化は、AIコンピューティングにおけるデータ移動のオーバーヘッドを根本から消滅させる可能性を秘めている。

圧倒的な性能指標とJEDEC規格を凌駕するデータ保持能力

今回のPOCチップによるテスト結果は、3D X-DRAMは容量拡大の代替案という枠を超え、性能面においてもデータセンター向けAIプロセッサの厳しい要求に耐えうる実力を持つことを実証している。

測定された主要なパフォーマンス指標において、読み出しおよび書き込みのレイテンシは10ナノ秒未満(<10 ns)という高速性を達成している。これは、立体構造を採用することでアクセス速度が犠牲になるのではないかという業界の懸念を払拭するものであり、従来のDRAMと同等の即応性を提供する。

とりわけ注目すべきは、その特筆すべきデータ保持能力(リテンションタイム)である。摂氏85度という過酷な熱環境下において、1秒以上のデータ保持を実現した。これは、業界標準化団体であるJEDECの規格が定める64ミリ秒という基準と比較して、15倍以上の圧倒的な改善に相当する。DRAMは構造上、キャパシタから徐々に電荷が失われるため、データを維持するための定期的な再書き込み(リフレッシュ動作)が不可欠である。リテンションタイムが1秒を超える水準に達することは、リフレッシュに必要な時間と電力消費を抑制し、読み書きアクセスの競合を劇的に削減することを意味する。結果として、システム全体の有効帯域幅の向上と大幅な省電力化に直結する。

同時に、隣接するセルへの干渉を示すビット線およびワード線のディスターバンス(干渉耐性)も摂氏85度で1秒以上を記録し、エンデュランス(書き換え耐性)は10の14乗サイクルを超える結果を示した。これにより、絶え間ないランダムアクセスが発生するAIの学習プロセスにおいても、実用化に向けた基礎的な信頼性が確保されていることが確認された。

台湾半導体エコシステムとの強固な結合と資本参加の構造的意義

NEO Semiconductorの今回の発表において、技術的成果と同等に重大な意味を持つのが、強固な半導体エコシステムを持つ台湾の主要プレイヤーとの連携が表面化したことである。概念実証の共同研究先であるNYCUやNIAR-TSRIとの提携に加え、Acerの創業者であり元CEO、さらには世界最大のファウンドリであるTSMCの取締役を20年以上にわたって務めたStan Shihが主導する戦略的投資ラウンドの完了が報告されている。

世界のロジック半導体およびメモリ製造の最前線である台湾のエコシステム中枢からの資金調達と支援は、3D X-DRAMに対する市場と業界からの強い信任の表れである。Stan Shihは、独自のイノベーションと強力なエンジニアリングの実行力、そして台湾の堅牢な半導体エコシステムが結集したことで今回のPOCが現実のものとなったと言及している。

この動きは単なる資金調達の枠を超え、次世代メモリの覇権争いにおける地政学的な意味合いも含んでいる。最先端のAIアクセラレータは実質的にTSMCのパッケージング技術(CoWoSなど)に依存しており、そこに組み込まれるメモリ規格が台湾の産学連携から生まれることは、供給網全体の垂直統合をさらに強固なものにする。世界各国の企業がAIメモリのボトルネック解消に向けて独自のアプローチを模索する中、製造エコシステムの中心地で実証された技術は、業界標準として急速に普及する優位性を持つ。

次世代メモリ技術の開発は、実験室での初期検証から商業的な量産化に至るまでの障壁が極めて高く、過去にも多くの有望なアーキテクチャが歩留まりや製造コストの壁(いわゆる「死の谷」)を越えられずに表舞台から消え去ってきた。しかし、NEO Semiconductorの戦略は自社で巨額の設備投資を行い工場を建設するのではなく、既存のグローバルなメモリメーカーへのスケーラブルなライセンス提供やパートナーシップモデルを想定している。成熟した3D NAND製造ラインを大きな設備変更なしに転用可能というアーキテクチャ上の特性と、台湾の産学連携によるエコシステムへの食い込みは、この量産の谷を乗り越えるための現実的かつ強力なロードマップを描き出している。

新たなアーキテクチャが描くハードウェアの未来

AIモデルのパラメータ数が指数関数的に増大を続ける中、メモリ帯域幅と容量の制約はハードウェア設計における最大の足かせとなっている。この課題に対し、IntelやSoftBankが支援する日本のSAIMEMORYによるZAM(Z-Angle Memory)の開発など、並行して進む代替技術の動きも活発化している。既存の2D DRAMの延長線上に物理的および経済的な限界が見える中、TechInsightsの専門家が指摘するように、メモリ業界全体が垂直方向への積層化という新しいパラダイムへと急速にシフトしている。

NEO Semiconductorの3D X-DRAMがこのまま量産化への課題を順調にクリアし、HBMの代替あるいは補完技術としてデータセンターのサーバー群や高度なエッジAIデバイスに導入された場合、AIシステム全体のコスト構造と電力効率は根本的に塗り替えられる。高価で複雑なシリコン貫通電極や特殊な2.5Dパッケージング技術に依存せず、既存の設備インフラストラクチャを活用して大容量かつ広帯域なメモリを安価に生産できる未来は、AIコンピューティングの持続可能性と普及を支える基盤技術となる。

概念実証から多層テストチップの開発、そしてアレイレベルの実装へと進む次のフェーズにおいて、世界の主要メモリベンダーがこの技術とどのようなパートナーシップを結ぶのか。ハードウェアアーキテクチャの進化の方向性を決定づける重大な局面に、業界全体が突入している。