2026年3月16日、カリフォルニア州サンノゼで開催された技術カンファレンス「GTC 2026」において、NVIDIAは新たなデータセンター向けプロセッサ「Vera CPU」の全貌を明らかにした。これまで人工知能の計算基盤として圧倒的なシェアを誇ってきた同社が、画像処理半導体(GPU)の領域を越え、汎用プロセッサの市場に対してかつてない規模の攻勢を仕掛ける。本稿では、Vera CPUが開発された技術的背景と、そこに組み込まれた独自のアーキテクチャを解き明かし、IntelやAMDが長年支配してきたサーバー市場の構造がどのように塗り替えられようとしているのかを見てみたい。

エージェント型AIの台頭が要求するプロセッサの復権

近年、人工知能の利用形態はテキスト生成やチャットボットから、自律的にタスクを計画し実行するエージェント型AI(自律型AIエージェント)へと急速に移行している。エージェントは抽象的な指示を受け取ると、外部ツールの呼び出し、データベースに対するSQLクエリの発行、そしてプログラムコードのコンパイルとサンドボックス環境での実行を自ら行う。

こうした複雑なワークロードは、並列計算に特化したGPUの演算能力をもってしても処理しきれない。NVIDIAのハイパースケールおよびHPC担当バイスプレジデントであるIan Buck氏が指摘するように、現代のエージェントはGPUからCPUへ処理を引き渡すことで成立している。GPUは一度に大量のデータを同じ命令で処理することには極めて優れている反面、条件分岐が連続し、多種多様なタスクを逐次的にこなすオーケストレーション処理は不得手としている。

数万規模のAIエージェントが独立して稼働し、それぞれが異なる推論と行動を繰り返す環境下では、システム全体のボトルネックはGPUの演算能力から、タスクを管理しデータを供給するCPUの処理能力へと移動した。創業者兼CEOのJensen Huang氏が述べる通り、プロセッサはモデルの実行を下支えする補助的な存在から、システム全体を駆動する主体へと変化している。NVIDIAはデータセンターにおけるコンピューティングの役割分担を根本から再定義する必要に迫られ、新たな設計思想に基づくシリコンを市場に投入した。

88基のカスタムコア「Olympus」とスレッド処理の再構築

Vera CPUの心臓部には、NVIDIAが独自に設計を施した88基の「Olympus」Armコアが搭載されている。前世代のGrace CPUが汎用的な設計を採用していたのに対し、Veraはより深く踏み込んだカスタムチューニングを施している。同世代のx86プロセッサと比較してコアあたりの性能を1.5倍に引き上げ、汎用プロセッサの半分の電力で2倍の効率を達成した。

性能飛躍の鍵となるのは、プロセッサ内部の命令処理機構の抜本的な改良だ。Olympusコアは10命令を同時に処理できる極めて広いデコードパイプラインを備え、「ニューラル分岐予測器」を組み込んでいる。プログラムの進行経路を先回りして推測する分岐予測は、現代のプロセッサ性能を左右する中核技術である。Veraの予測器は1サイクルあたり2つの分岐を同時に予測し、予測外れによる処理の遅延を最小限に抑え込む。

さらにNVIDIAは「空間的マルチスレッディング(Spatial Multithreading)」という特異なアプローチを導入した。一般的なサーバープロセッサで用いられる同時マルチスレッディング技術は、実行ユニットなどの演算資源を極めて短い時間で区切り、複数のスレッドに交互に割り当てるタイムスライス方式を採用している。これに対しVeraは、パイプラインの構成要素を物理的に分離し、リソースの奪い合いを発生させずに2つのタスクを単一コア内で完全同時に実行する。この構造は、クラウド事業者が多数の顧客にインフラを提供するマルチテナント環境において、他の処理に足を引っ張られることなく、常に一定のパフォーマンスを維持できるという決定的な利点をもたらす。

メモリ帯域の飛躍とNUMAアーキテクチャの排除

どれほど強力な演算コアを備えていても、処理すべきデータが届かなければプロセッサは待機状態に陥る。頻繁にデータを取得してコードを実行するAIエージェントの処理において、メモリの帯域幅は極めて重要である。Vera CPUは一般的なサーバーで用いられる規格を採用せず、ノートパソコンなどに搭載されるLPDDR5Xメモリをデータセンター向けに最適化したSOCAMMモジュールとして実装した。

この決断により、プロセッサ1基あたり最大1.5TBのメモリ容量を確保しつつ、1.2 TB/sという桁違いの帯域幅を実現している。これはIntelのデータセンター向け最上位プロセッサが記録する825 GB/sや、AMDの同等製品が示す600 GB/s前後の数値を大きく上回る。

特筆すべきは、全88コアが単一のドメインに配置されている点である。多コア化が進む現代のx86プロセッサの多くは、コアとメモリの接続領域を複数に分割するNUMA(Non-Uniform Memory Access)構成をとる。この構成では、あるコアが自身の所属しない領域のメモリにアクセスする際に遅延が発生し、性能が低下するという構造的な弱点が存在する。Veraは第2世代のNvidia Scalable Coherency Fabricと呼ばれるメッシュネットワークを用いて全コアを均質に接続し、NUMA特有の複雑さを完全に排除した。フル稼働時でも各コアに平均13.6 GB/s、特定のコアには最大80 GB/sの帯域幅をダイナミックに供給できるため、ソフトウェア開発者はデータの配置を意識することなくシステム性能を限界まで引き出すことが可能になる。さらに、コンフィデンシャルコンピューティングの完全なサポートにより、セキュリティ要件の厳しいクラウド環境にも適応している。

ラック単位で提供される超高密度な液冷インフラストラクチャ

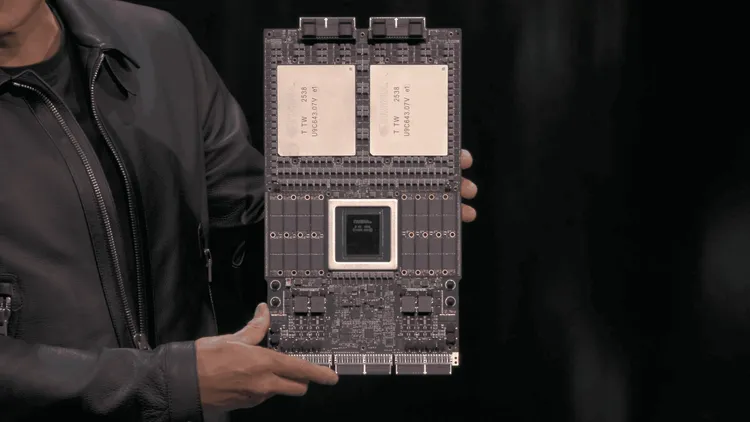

プロセッサ単体の革新に加え、NVIDIAはシステム全体の実装形態においても新たな基準を打ち出している。Vera CPUは、256基のチップを一つのラックに集約した液冷システムとして展開される。MGXモジュラーリファレンスアーキテクチャに基づくこの巨大なインフラは、400TBという広大なメモリ空間を備え、22,500もの独立したCPU環境を同時にフルパフォーマンスで稼働させる能力を持つ。

ラック内部にはネットワークやストレージの管理を代行する64基のBlueField-4データ処理ユニットとConnectX SuperNICが組み込まれており、プロセッサからインフラストラクチャの維持に伴う通信負荷を完全に取り除く。これにより、Veraの演算資源はAIエージェントの推論や強化学習といった本来の目的に完全に注力できる。

高度な集積化は従来型の空冷システムでは到底対処できない発熱を伴うため、このラックは設計の初期段階から液冷を前提としている。これはAIファクトリーの冷却手法が、部屋全体の空調からラックやチップを直接冷却する方式へと不可逆的に進化したことを明確に示している。

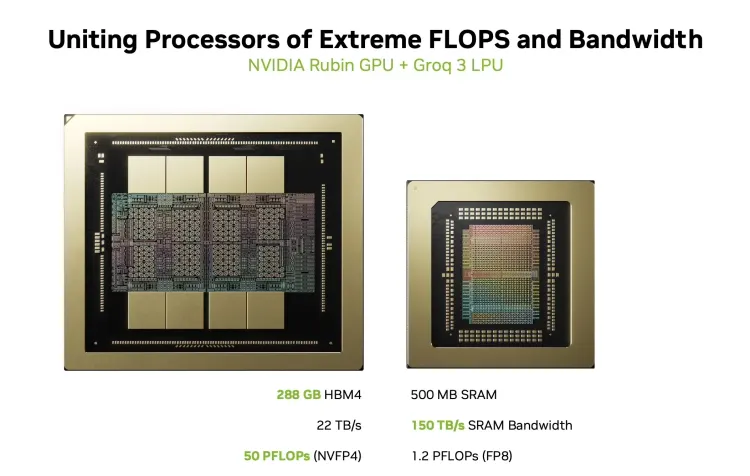

システムはGPUとの連携も極限まで高められている。Vera Rubinプラットフォームにおいては、CPUとGPUがNVLink-C2Cインターコネクト技術によって接続される。最新のPCIe Gen 6規格の7倍に相当する双方向1.8 TB/sという驚異的な帯域幅により、互いのメモリ空間を共有する際の待ち時間は事実上消滅する。

既存の勢力図を書き換える次世代データセンターの覇権

Vera CPUの市場投入は、IntelやAMDが長らく主導してきた伝統的なプロセッサ市場に対する直接的な挑戦だ。NVIDIAはこれまでも自社のGPUの性能を最大限に引き出すためのプラットフォームの一部としてプロセッサを提供してきたが、Veraは単独のコンピューティング基盤として市場に供給される。

この戦略はすでに市場で大きな動きを生み出している。MetaはNVIDIAのプロセッサを自社のデータセンターで大規模に展開する計画を明らかにしており、OracleやAlibaba、ByteDanceといった巨大クラウド事業者、さらにはCoreWeaveやNebiusといったAI特化型のインフラプロバイダーも導入を決定している。テキサス・アドバンスト・コンピューティング・センターをはじめとする米国の主要な国立研究所の導入計画は、このプロセッサがAI分野にとどまらず、科学技術計算の領域においても高い競争力を持つことを示している。

実際のアプリケーション環境でも劇的な性能向上が報告されている。AIネイティブなソフトウェア開発環境を提供するCursorは、コーディングエージェントの応答性を高めるためにVeraの採用を決定した。データストリーミング基盤を手掛けるRedpandaは、互換ワークロードの実行において既存のシステムに対し5.5倍という圧倒的な低遅延を記録したと公表している。

コンピューティングの主戦場が単純なバッチ処理から、推論と行動を連続して行う自律的プロセスのオーケストレーションへと移行する中で、基盤となるハードウェアのあり方もまた劇的な変容を求められている。エージェンティックAIの要求水準を満たすためにゼロから再構築されたVera CPUの登場は、汎用プロセッサが支配してきたデータセンターの歴史に明確な区切りをつける出来事なのだ。

Sources