半導体製造最大手のTSMCが、2028年量産開始予定の次世代プロセスノード「A14」において、最先端とされるHigh-NA EUV(高開口数 極端紫外線)リソグラフィ技術の導入を見送る方針を明らかにした。コスト効率を最優先し、実績のある既存技術の改良で対応する構えだが、この決断はライバルであるIntel Foundryの先行を許容する可能性をはらんでいる。

TSMCの戦略的判断:A14では既存技術を継続

TSMCの上級副社長であるKevin Zhang氏は、米国の技術シンポジウムにおいて、同社がA14ノード(1.4nmプロセスに相当すると見られる)のパターニングにHigh-NA EUVリソグラフィを使用しない計画であることを明かした。 A14ノードの量産は2028年に開始される予定であり、TSMCは現行の0.33-NA EUVツールとマルチパターニング技術を組み合わせることで、2nm世代からA14世代に至るまで、性能、歩留まり、集積度の目標を達成できると判断している。

Zhang氏は、「各技術世代において、我々はマスク(回路パターンを転写するための原版)枚数の増加を最小限に抑えるよう努めている。これはコスト効率の良いソリューションを提供するために非常に重要だ」と述べ、今回の決定がコスト管理と製造工程の簡素化を重視した結果であることを示唆した。 つまり、現時点でのHigh-NA EUV導入は、コストに見合うメリットがないと判断したわけである。

このアプローチは、より複雑な回路パターンを形成するために、1回の露光で済むHigh-NA EUVを用いる代わりに、既存の0.33-NA EUVツールで複数回の露光(マルチパターニング)を行うことを意味する。TSMCは、この方法によってHigh-NA EUVの極めて高い精度を必要とせずに、同等の設計複雑性を維持できると考えているようだ。

なぜHigh-NA EUVを見送るのか? 立ちはだかるコストの壁

TSMCがHigh-NA EUV導入に慎重な姿勢を示す最大の理由は、その莫大なコストにある。

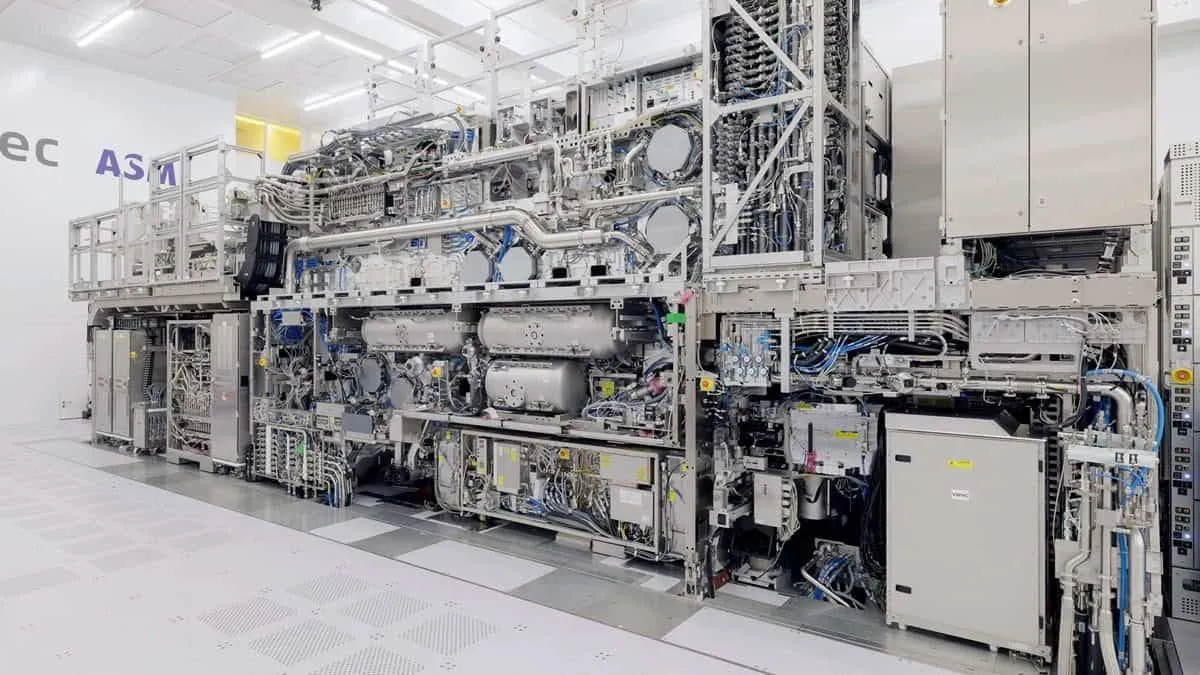

- 装置価格の高騰: High-NA EUVリソグラフィを実現するASML社製の最新リソグラフィマシン「Twinscan EXE:5000」は、1台あたり約3億8000万ドル(約600億円)と、従来のEUV装置(0.33-NA)と比較しても非常に高価である。 半導体工場には多数のリソグラフィマシンが必要となるため、導入には巨額の設備投資が求められる。

- 運用コストの増加: High-NA EUVは、より高い露光量(露光に必要な光エネルギー)を必要とし、一般的にスループット(単位時間あたりの処理能力)が既存のツールよりも低い傾向にある。 さらに、IBMの研究者による最近の報告では、High-NA EUVによる1回の露光コストは、従来の低NA(0.33-NA)EUV露光の最大2.5倍に達する可能性があると指摘されている。

- コスト効率の観点: TSMCの見積もりでは、A14ノードでHigh-NA EUVを採用した場合、従来のEUVを用いた手法と比較して最大2.5倍のコスト増を招く可能性があるという。 これは最終製品の価格に跳ね返り、特にコンシューマー向け製品への採用を困難にする可能性がある。

一方で、非常に複雑な回路層においては、複数回の低NA露光(例えば4回のマスクを使用)を行うよりも、1回のHigh-NA露光の方が、ウェハー全体のコストを約1.7倍から2.1倍削減できる可能性も指摘されている。 しかし、業界アナリストのSemiAnalysisは、High-NA EUVと既存技術の全体的なコストが同等になるのは2030年頃になると予測しており、現時点での導入にはまだコスト的なハードルが高いと見ている。

High-NA EUVとは? 微細化を推し進める次世代技術

ここで、High-NA EUVリソグラフィ技術について簡単に触れておこう。リソグラフィは、シリコンウェハ上に微細な回路パターンを焼き付ける半導体製造の中核工程であり、その精度がチップの性能や集積度を左右する。

EUV(Extreme Ultraviolet:極端紫外線)リソグラフィは、従来のArF液浸露光よりもさらに波長の短い光(13.5nm)を用いることで、より微細な回路形成を可能にした技術である。現在主流となっているのは、NA(Numerical Aperture:開口数)が0.33のEUVリソグラフィだ。

NAとは、レンズが集める光の角度範囲を示す指標であり、この値が大きいほど解像度が高まり、より細かいパターンを形成できる。High-NA EUVは、このNA値を0.55に引き上げた次世代技術であり、理論上は0.33-NA EUVよりもさらに微細な回路を描くことが可能となる。

しかし、NA値を上げることは技術的に非常に困難であり、巨大で複雑な光学系や、より強力な光源が必要となる。これが前述のような装置コストや運用コストの増大につながっている。

ライバルIntelとの戦略差:先行するIntel、追うTSMC?

TSMCがHigh-NA EUVの導入を見送る一方で、最大のライバルであるIntel Foundry(Intelの半導体受託製造部門)は、より積極的な姿勢を見せている。Intelは、2025年にも量産開始を目指す「Intel 18A」プロセス(1.8nm相当)でHigh-NA EUVを導入する計画を明確にしている。

IntelはすでにASMLから最新のHigh-NA EUV装置「Twinscan EXE:5000」を受領し、18Aに続く「Intel 14A」ノードの開発において、この装置を用いて既に30,000枚以上の試験ウェハを処理したと報告されている。 これは、IntelがHigh-NA技術の習熟と量産適用に向けて着実に歩を進めていることを示している。

TSMCもHigh-NA EUV技術を完全に諦めたわけではない。同社はA14に続く「A14P」と呼ばれる改良版ノード(おそらく2029年頃)でのHigh-NA導入を計画しているとされる。 しかし、Intelが計画通り18AでHigh-NAを導入すれば、TSMCはHigh-NA技術の本格導入においてIntelに最大で4年程度の遅れをとる可能性がある。

これは、長年にわたり半導体微細化の先頭を走ってきたTSMCにとって、注目すべき戦略転換と言えるかもしれない。Intelや一部のDRAMメーカーは、すでに最も重要な層に限定してHigh-NAを選択的に採用し始めており、TSMCはこれらの企業に対して技術採用の面で後れを取る形となる。

業界への影響と今後の展望:コスト効率か、技術的優位か

TSMCの今回の決定は、半導体業界における技術革新とコスト効率のバランスを巡る永遠の課題を改めて浮き彫りにした。TSMCは、実績のある技術を最大限に活用し、コストを抑えることで顧客に価値を提供しようとしている。これは、特に先端プロセスが高コスト化する中で、現実的かつ合理的な戦略とも言えるだろう。

しかし、一方でIntelがHigh-NA EUVの先行導入によって技術的な優位性を確立し、ファウンドリ市場でのシェア拡大を狙ってくる可能性も否定できない。もしIntel 18Aが計画通りに立ち上がり、高性能かつコスト競争力のあるチップを供給できれば、TSMCの牙城に迫る存在となり得る。

今後の焦点は、以下の点に集まるだろう。

- TSMC A14の実力: 0.33-NA EUVとマルチパターニングで、目標とする性能・コスト・歩留まりを達成できるか。

- Intel 18A/14Aの進捗: High-NA EUVを用いた量産プロセスを計画通りに立ち上げ、その優位性を示すことができるか。

- High-NA EUVのコスト動向: 装置の価格や運用コストが今後どのように変化していくか。SemiAnalysisの予測通り、2030年頃にコスト同等性が実現するのか。

- TSMC A14Pの詳細: TSMCが計画するHigh-NA導入プロセスがいつ、どのような形で登場するのか。

TSMCの選択は、短期的にはコスト効率を重視した堅実な道に見える。しかし、長期的に見て技術的リーダーシップを維持できるか、そしてIntelの挑戦をどう受け止めるのか。今回の決定は、未来の半導体業界の勢力図を左右する可能性のある、重要な岐路と言えるだろう。

Source

- Bits and Chips: TSMC skips high-NA for A14