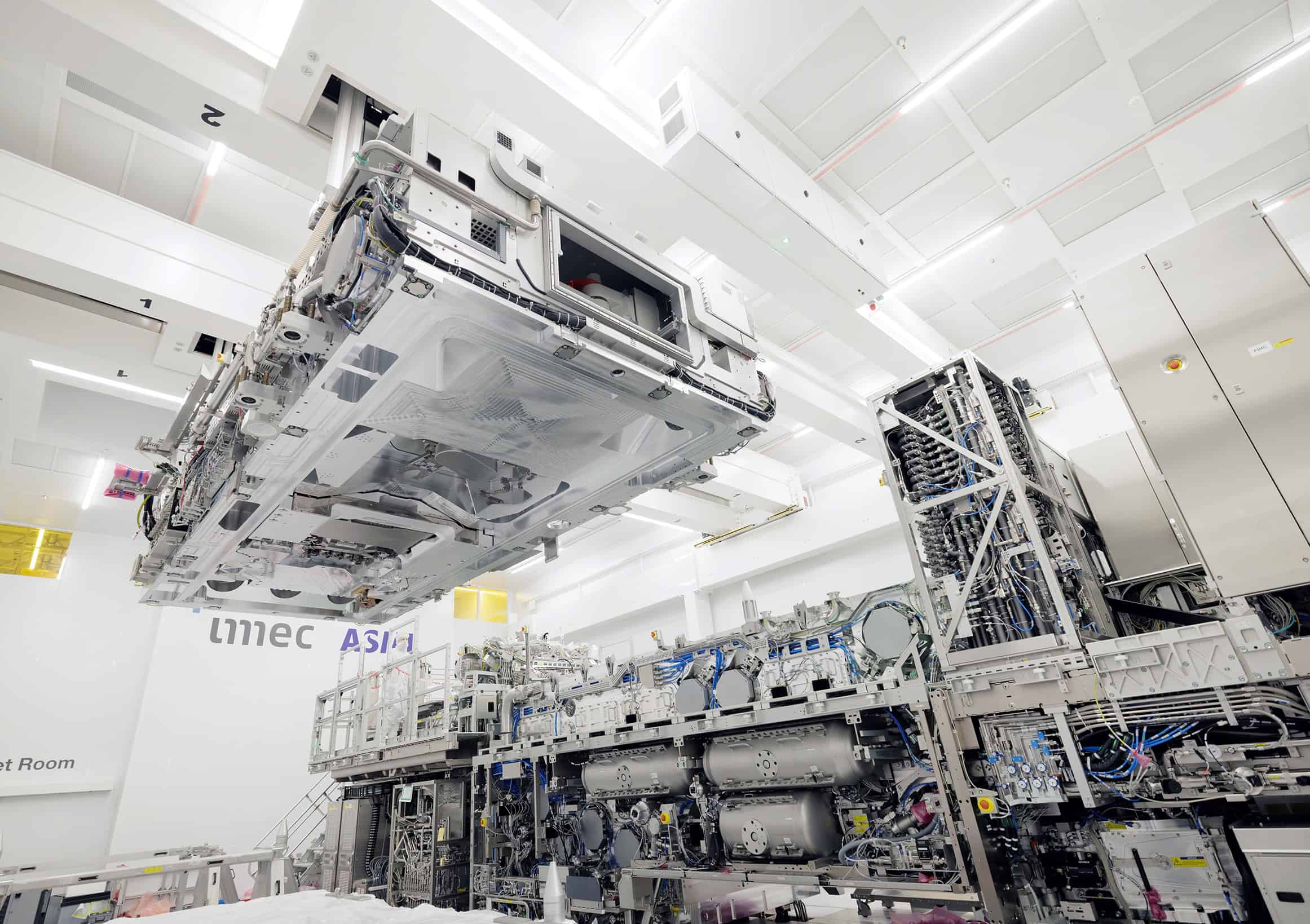

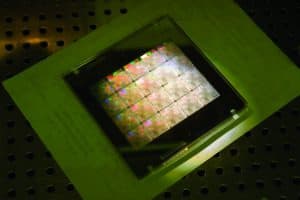

台湾の半導体大手TSMCが、次世代の半導体製造技術の核心となるHigh-NA EUVリソグラフィ装置を9月に導入する計画であることが明らかになった。この装置は、オランダのASML社が開発した最新鋭の半導体製造装置で、より微細な回路パターンを描画することが可能となり、2nm以降の先端プロセス技術の開発に不可欠とされている。

TSMCのHigh-NA EUV装置導入計画の詳細

台湾の業界筋によると、TSMCは9月末までに、ASML社製のHigh-NA EUV装置を受け取る予定だという。この装置の価格は約4億ユーロ(約600億円)を超えると推定されており、半導体製造装置としては極めて高額なものとなっている。

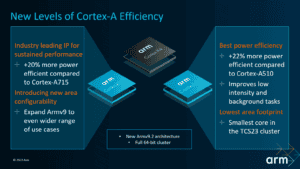

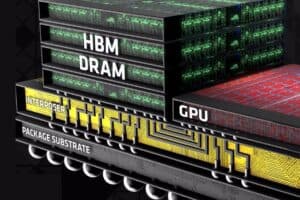

High-NA EUV(高開口数極端紫外線)リソグラフィ装置は、従来のEUV装置よりもさらに微細な回路パターンを描画することができ、より高性能で省電力な半導体チップの製造を可能にする。TSMCはこの装置を新竹にある同社のグローバル研究開発センターに設置し、次世代プロセス技術の開発に活用する計画だ。

装置の巨大さと精密さから、TSMCは特別な輸送計画を立てる必要があるとされている。装置は分解できないため、夜間に特別な経路で輸送される可能性が高い。これは、交通渋滞を避け、精密機器の安全な輸送を確保するためだ。

TSMCの張曉強副共同最高執行責任者(COO)は以前、「High-NA EUVの性能は気に入っているが、価格が高すぎる」と述べていた。しかし、今回の導入決定により、TSMCがASMLと価格交渉を行い、一定の譲歩を引き出した可能性が高い。業界筋によると、TSMCは通常価格から最大20%の割引を獲得した可能性があるという。

半導体業界の競争激化とTSMCの戦略

High-NA EUV装置の導入は、TSMCが半導体製造技術の最先端を走り続けるための重要な一手となる。しかし、競合他社もTSMCの牙城を崩すべく、この次世代半導体製造装置の導入を急いでいる。

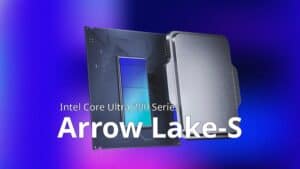

Intelは既に2023年末にHigh-NA EUV装置を受け取り、2024年初頭に初めて稼働させたと発表している。Intelは2025年にも同装置を生産に投入する計画を明らかにしており、プロセス技術でのリーダーシップ奪回を目指している。

一方、TSMCのもう一つの主要な競合相手であるSamsungは、2024年第4四半期か2025年にHigh-NA EUV装置を受け取る予定だとされている。

TSMCは現在のところ、2nmクラスのN2プロセスと1.6nmクラスのA16プロセスまでは従来のEUV装置で対応する計画だ。High-NA EUV装置の本格的な導入は、早くても2028年以降のA14(1.4nmクラス)プロセスからになると見られている。

この慎重なアプローチは、High-NA EUV装置の導入に伴う技術的課題や、チップ設計者と製造者双方にとっての新たな挑戦を考慮したものだと考えられる。TSMCは現在、世界のEUV生産能力の約65%を保有しており、この優位性を活かしながら、次世代技術への移行を進めていく戦略を取っているようだ。

半導体の微細化競争が激化する中、High-NA EUV装置の導入は、TSMCが業界のリーダーシップを維持するための重要な一手となる。今後、この装置を用いた研究開発の進展と、実際の製品への応用が注目される。

Sources

コメント