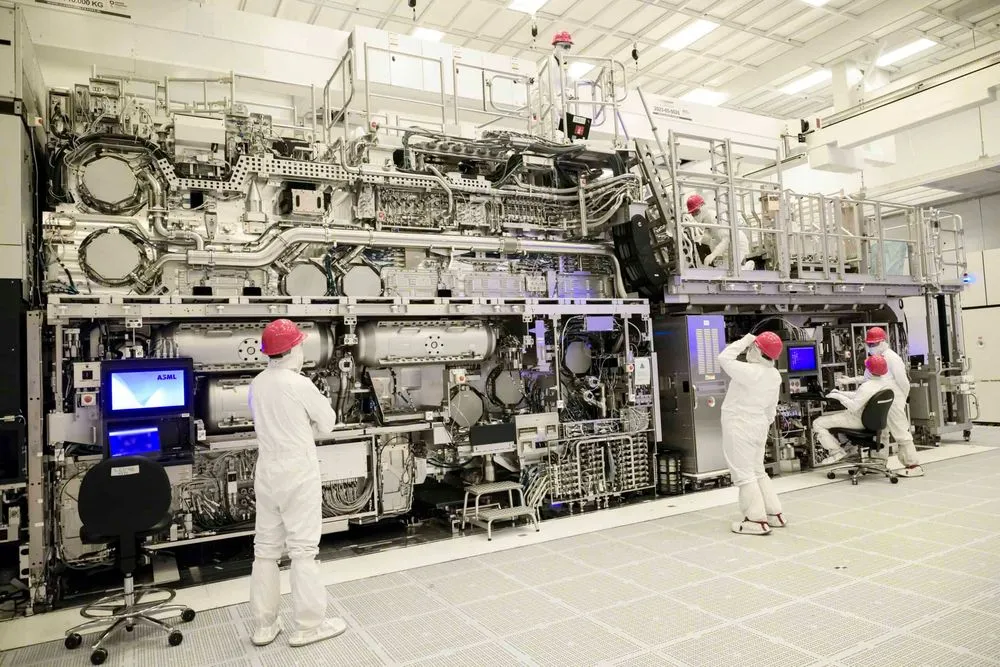

Intelのファウンドリ部門であるIntel Foundryは、ASML製の第2世代High-NA(高開口数)EUV露光装置「TWINSCAN EXE:5200B」の受け入れテストが完了したと発表した。これは研究開発(R&D)フェーズから、商業的な大量生産(HVM)フェーズへと、次世代リソグラフィ技術が確実に歩を進めたことを示すマイルストーンと言える物だ。

本稿では、この「EXE:5200B」が従来の装置と何が異なるのか、そして2027〜2028年と予測される量産開始に向け、半導体業界の勢力図がどう塗り替わろうとしているのかを見ていきたい。

「実験室」から「工場」へ:EXE:5200Bが持つ決定的意味

これまでのHigh-NA EUV導入のニュースは、主に「技術的な可能性の検証」に主眼が置かれていた。しかし、今回Intelが完了した「EXE:5200B」の受け入れテストは、意味合いが全く異なる。

初代「EXE:5000」との明確な差別化

Intel Foundryが以前導入した初代機「TWINSCAN EXE:5000」は、主にプロセス開発やレジスト(感光材)の評価を行うためのR&D向けシステムであった。対して、今回焦点となっている「EXE:5200B」は、明確に「量産(Manufacturing)」を見据えた仕様となっている。

Intelの公式ブログによれば、この第2世代機には以下の決定的な進化が見られる。

- スループット(生産性)の大幅向上: 1時間あたり175枚(wph)のウェハー処理能力を実現。

- オーバーレイ精度の深化: 0.7nmという極限の重ね合わせ精度を達成。

- 光源出力の強化: より高速な露光と、パターン品質の向上を両立。

なぜ「毎時175枚」が重要なのか

ここで注目すべきは「175 wph」という数値である。従来のEUV露光装置(Low-NA)と比較しても、High-NAは光学系の複雑化によりスループットが低下するリスクが懸念されていた。半導体製造において、スループットはコスト競争力に直結する。

1台あたり数百億円とも言われる超高額な装置を導入しても、処理枚数が少なければチップ1枚あたりのコストは跳ね上がる。今回、EXE:5200Bが175 wphという、既存の量産ラインと遜色ない(あるいはそれに近い)処理能力を示したことは、High-NA EUVが「採算の取れる技術」になりつつあることを証明している。これは、投資家や顧客(ファブレス企業)に対する強力なメッセージだ。

量産を支える「地味だが重要」な革新

Intelの技術ブログからは、単なるスペック向上以上の、現場レベルでの「量産適合性(Manufacturability)」への執念が見て取れる。

熱安定性と物流の最適化

一般的にニュースの見出しにはなりにくいが、今回Intelが強調しているのが「新しいウェハーストッカー構造」である。

ナノメートルレベルの加工を行うHigh-NA EUVにおいて、最大の敵の一つは「熱」だ。ウェハーがわずかに熱膨張するだけで、0.7nmというオーバーレイ精度は容易に破綻する。EXE:5200Bでは、ウェハーの保管・搬送時の熱安定性を高めることで、マルチパターニングや多重露光といった複雑な工程においても、「ドリフト(ズレ)」を最小限に抑える設計がなされている。

これは、実験室で「1回だけ成功すればいい」という段階を脱し、工場で「何万回も安定して成功させる」ための機能実装である。

線幅粗さ(LWR/LER)の低減と光源パワー

EUV光源の出力向上は、単に処理速度を上げるだけではない。十分な光量(ドーズ量)をレジストに与えることで、パターンの「コントラスト」を鮮明にし、配線の端がギザギザになる現象(ラインエッジラフネス:LER)や線幅のばらつき(LWR)を抑制する効果がある。

微細化が進むにつれ、このわずかな「ギザギザ」が配線抵抗の増大や断線を引き起こす致命傷となる。高出力光源の搭載は、AI時代に求められる高性能ロジック半導体の歩留まりを確保する上で不可欠な要素なのだ。

次世代トランジスタ「2DFET」との統合戦略

今回のIntelの発表で興味深いのは、露光装置の話とセットで、次世代トランジスタ材料に関する研究成果(IEDMでの発表)に触れている点だ。ここにはIntelの明確な技術戦略が隠されている。

シリコンの限界を超える「2次元材料」

現在主流のGAA(Gate-All-Around)構造の次に来る技術として、Intelは原子数個分の厚みしかない「2次元材料(2D materials)」を用いたトランジスタ(2DFET)の開発を進めている。具体的には、遷移金属ダイカルコゲナイド(TMDs)と呼ばれる材料群だ。

Intelはベルギーの研究機関Imecと共同で、300mmウェーハ上での2DFET製造プロセスを実証した。ここで鍵となるのが「ダマシン型トップコンタクト(Damascene-style top contacts)」技術である。

High-NA EUV × 新材料の相乗効果

High-NA EUVによって極限まで微細な回路パターンを描くことができても、その回路を構成する「材料」が電気を正しく流せなければ意味がない。シリコンが物理的限界(原子レベルのスケールによる性能低下)に近づく中、Intelは「描画技術(High-NA)」と「材料技術(2DFET)」の両輪を同時に完成させようとしている。

ブログ内でこれらを同時に語る意図は明確だ。「我々は微細な線を引くだけではない。その線の中で最高性能を発揮するトランジスタを作る準備もできている」という、システムレベルでの技術的優位性の主張である。

2027-2028年:量産へのロードマップと市場への影響

ASML CEO、Christophe Fouquet氏の発言によれば、High-NA EUVを用いた大量生産(High Volume Manufacturing)の開始時期は2027年から2028年と予測されている。

Intel “14A” プロセスとその先

このタイムラインは、Intelが計画している「Intel 14A(1.4nm相当)」プロセス以降のロードマップと合致する。2025〜2026年にかけて顧客との共同テストやダウンタイム(稼働停止時間)の最小化に取り組み、2027年に本格的な量産体制に入るというシナリオだ。

競合他社(TSMC, Samsung)との距離感

IntelはHigh-NA EUVの導入において、TSMCやSamsungに対し先行者利益を狙う「ファーストムーバー」戦略をとっている。TSMCは既存のLow-NA EUVのマルチパターニング技術で当面の微細化(A16プロセス等)を乗り切る慎重な姿勢を見せているが、2027年以降の超微細領域ではHigh-NAが必須になると見られている。

IntelがこのEXE:5200Bを早期に「使いこなす」知見を蓄積できれば、1.4nm世代以降のファウンドリビジネスにおいて、AppleやNVIDIAといった主要顧客に対し、強力な技術的差別化要因を提示できることになる。

将来の「Hyper NA」への布石

さらにASMLは、2030年代に向けて、現在のNA(開口数)0.55を超える「Hyper NA(NA 0.75以上)」の研究も進めている。IntelとASMLの現在の緊密な連携は、このさらに先の未来においても、Intelが最優先で次世代機を手に入れるための布石となっている可能性が高い。

AI時代のハードウェア覇権を握る鍵

今回のニュースを単なる「装置のテスト完了」と捉えるのは早計だ。ここから読み取るべきは以下の3点である。

- High-NA EUVは「実用段階」に入った: 175 wphというスループットと0.7nmの精度は、実験室のスペックではなく、工場のスペックである。

- Intelの統合的アプローチ: 露光技術だけでなく、2次元材料やウェーハ搬送技術を含めたトータルな製造プロセスの革新が進んでいる。

- 2027年が分水嶺: AIチップの需要が爆発的に増加する中、High-NA EUVによる量産が始まる2027年頃、半導体の性能曲線は再び急角度で上昇する可能性がある。

「ムーアの法則」の延命、あるいは再定義に向けた戦いは、物理学の限界に挑む総力戦の様相を呈している。Intel Foundryがこの「二代目」の巨人を手なずけ、安定稼働させられるかどうかが、今後の世界のテクノロジーインフラの進化速度を決定づけると言っても過言ではないだろう。

Sources