日本の半導体製造ベンチャーRapidusが開発中の2nmプロセス「2HP」が、業界の巨人TSMCの次世代プロセス「N2」と実質的に同等のロジック密度を達成したことが報じられている。これは、長らく台湾と韓国のメーカーが支配してきた最先端半導体製造の勢力図を塗り替える可能性を秘めた、極めて重要な技術的マイルストーンと言えるだろう。

半導体地政学を揺るがす日本の挑戦

半導体は現代社会の神経系であり、その製造能力は国家の経済安全保障と技術的優位性を直接的に左右する。この核心技術において、日本はかつて世界のリーダーであったが、2000年代以降、その地位をTSMCとSamsungに明け渡してきた。この状況を打破すべく、日本政府と主要企業8社が結集して設立されたのがRapidusである。

同社が掲げる目標は、2027年に2nm世代の量産を開始するという野心的なものだ。多くの専門家がその実現性に懐疑的な視線を向ける中、今回明らかになったロジック密度のデータは、Rapidusの技術開発が単なる目標ではなく、現実的な軌道に乗っていることを示す最初の具体的な証と言える。

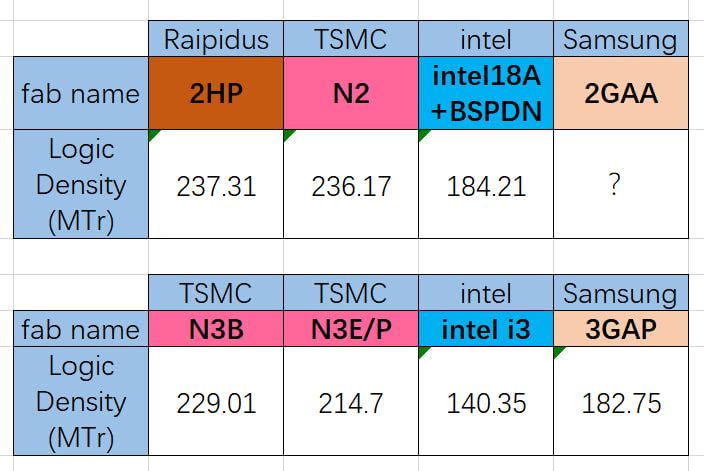

2nmプロセスにおけるロジック密度の徹底比較

最先端プロセスの性能を評価する上で、ロジック密度は最も重要な指標の一つである。これは、単位面積あたりにどれだけ多くのトランジスタを実装できるかを示すもので、MTr/mm²(Mega-transistors per square millimeter、1平方ミリメートルあたりのトランジスタ数百万個)という単位で表される。密度が高いほど、より小型で、高性能かつ電力効率に優れたチップを製造できる。

MTr/mm²という指標の本質:単なる集積度ではない

ロジック密度は、半導体プロセスの進化を測る最も基本的な指標の一つだ。それは、トランジスタ構造、セルライブラリの設計、配線技術、そして製造プロセスの成熟度といった、無数の技術的選択が凝縮された結果である。特に重要なのが、スタンダードセルと呼ばれる論理回路の基本単位の設計だ。

- HD (High Density) セル: トランジスタを可能な限り高密度に配置することに特化したセル。面積効率は最大化されるが、個々のトランジスタの性能(スイッチング速度)は必ずしも最高ではない。主にCPUのキャッシュメモリ(SRAM)周辺や、高い並列処理が求められるロジック部に用いられる。

- HP (High Performance) セル: トランジスタ性能を最大化するために、より大きな駆動電流を確保できるよう設計されたセル。密度は犠牲になるが、高速な動作が求められるCPUのコア部分などに不可欠である。

今回比較されている数値は、各社が「HDセルライブラリ」を用いて算出した理論値に近いものと推測される。つまり、これは各プロセスが達成しうる「最大集積度」を比較していると理解すべきだ。

Rapidus “2HP” vs TSMC “N2” – 驚異の技術的同等性

今回報告されたデータは衝撃的だ。

- Rapidus 2HP: 237.31 MTr/mm²

- TSMC N2: 236.17 MTr/mm²

両者の差はわずか0.5%未満であり、これは測定誤差や算出基準の違いを考慮すれば、事実上の「技術的同等性(Parity)」が達成されたことを意味する。これは、Rapidusがトランジスタの基本構造であるGAA(Gate-All-Around)技術の習得において、業界のリーダーであるTSMCと肩を並べるレベルに到達したことを強く示唆している。GAAは、従来のFinFET構造よりもゲートがチャネルを全方向から囲むことで、リーク電流を効果的に抑制し、さらなる微細化を可能にする次世代トランジスタ技術だ。この複雑な3次元構造を安定して製造する技術力こそが、2nm世代の核心であり、Rapidusがその関門を突破しつつあることに外ならない。

Intel “18A”の密度が低い理由 – 設計思想の違いを読み解く

一方で、同じく次世代プロセスとして注目されるIntelの18Aは、異なる数値を示している。

- Intel 18A + BSPDN: 184.21 MTr/mm²

この数値はRapidusやTSMCと比較して約22%低い。これを単純に「Intelの技術的劣位」と結論付けるのは早計である。この背景には、Intelの野心的な技術的選択と、それに伴うトレードオフが存在する。

Intel 18Aの最大の特徴は、BSPDN(Backside Power Delivery Network、裏面電源供給ネットワーク) の採用にある。これは、従来チップの表面(トランジスタが存在する側)に形成されていた電源供給用の配線網を、ウェハーの裏面に移動させる革新的な技術だ。

このBSPDNの採用は、アーキテクチャに二つの大きな影響を与える。

- 性能向上: チップ表面の配線層から電源線がなくなることで、信号線の配線に余裕が生まれる。これにより、信号線同士の干渉(クロストーク)が減り、配線抵抗も低減できるため、より高速で安定した信号伝達が可能になる。これは、電力効率(Performance per Watt)の向上に直結する。

- 密度測定上の不利: 一方で、BSPDNを実現するためには、ウェハー裏面と表面を繋ぐビア(TSV: Through-Silicon Viaに類似した構造)などが必要となり、これがトランジスタの配置に一定の制約を与える。HDセルライブラリを用いて理論上の最大密度を計算する際、この制約が考慮されると、見かけ上のMTr/mm²は低くなる傾向がある。

つまり、Intelは純粋なトランジスタ密度をわずかに犠牲にしてでも、電力効率と実動作性能を最大化するという明確な設計思想に基づきBSPDNを採用した。これに対し、RapidusとTSMCは、現時点ではよりコンベンショナルな表面電源供給を前提に、まずはトランジスタの集積度を極限まで高めるアプローチを採っている。どちらの選択が最終的に優れた製品を生み出すかは、実際のチップ設計とアプリケーションの要求によって変わってくるだろう。

製造戦略とエコシステム – Rapidusの独自性と課題

技術的な同等性は、あくまでスタートラインに過ぎない。半導体ビジネスで成功を収めるには、優れた製造プロセスと、それを支えるエコシステムの構築が不可欠だ。

「全工程枚葉式」が持つ戦略的意味

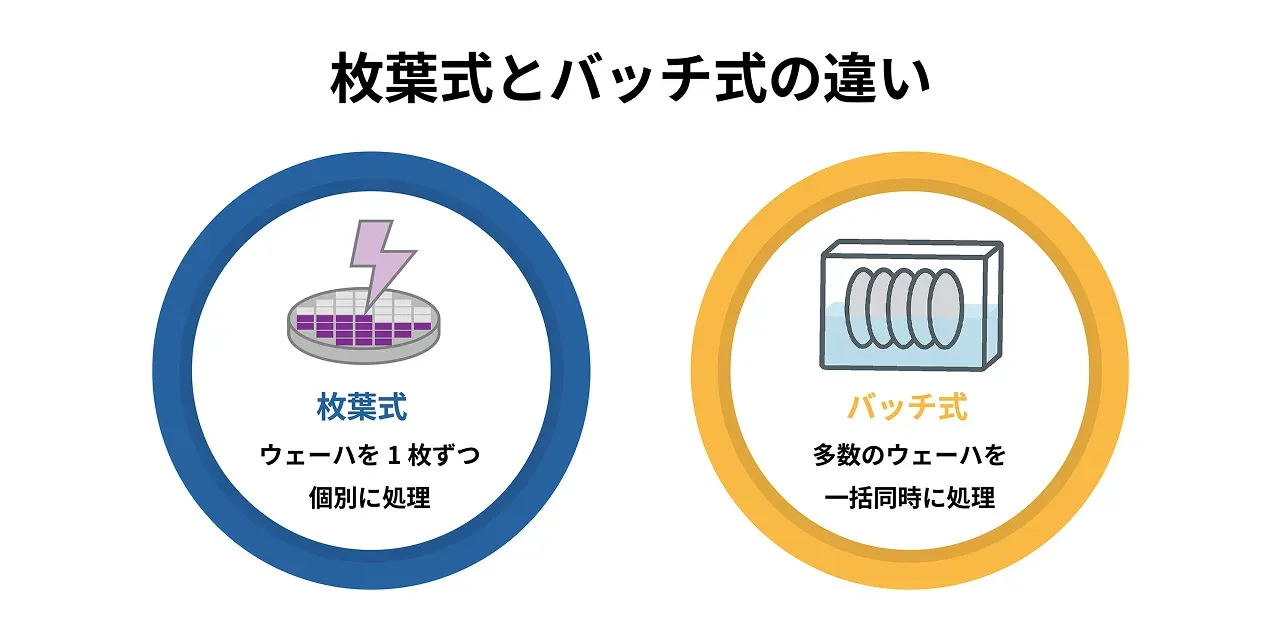

Rapidusは、従来の多数枚のウェハーをまとめて処理するバッチ方式とは異なり、「枚葉式」と呼ばれる手法を採用していると報じられている。これは、ウェハーを一枚ずつ処理することで、各工程での精密な制御と迅速なフィードバックを可能にするアプローチだ。

この手法は、量産初期の歩留まり向上や、開発サイクルの短縮に大きな利点をもたらす可能性がある。特に、AIアクセラレータや特定用途向けASIC(Application Specific Integrated Circuit)など、少量多品種のカスタムチップ市場において、顧客の要求に柔軟かつ迅速に対応できるという競争優位性に繋がるかもしれない。これは、大規模量産でスケールメリットを追求するTSMCとは異なる市場セグメントを狙う、巧みな戦略とも解釈できる。

PDK提供と顧客獲得という巨大な壁

どれほど優れたプロセス技術があっても、それを使ってチップを設計してくれる顧客がいなければビジネスは成り立たない。その鍵を握るのがPDK(Process Design Kit)だ。PDKは、ファウンドリの製造プロセスに関する詳細な情報(トランジスタの電気的特性、配線層の物理的制約など)をまとめた設計データ群であり、AppleやNVIDIAのようなファブレス企業はこれを用いてチップを設計する。

Rapidusは、このPDKを2026年初頭に顧客へ提供開始する計画だ。このPDKが、SynopsysやCadenceといった主要なEDA(Electronic Design Automation)ツールと完全に互換性を持ち、かつ信頼性の高いものであることを証明できるか。そして、最初の「ビッグカスタマー」を獲得できるか。これらが、2027年の量産開始に向けた最大の試金石となる。

半導体業界は新たな競争の時代へ

Rapidusの2nmプロセスがTSMC N2と同等のロジック密度を達成したというニュースは、単なる一企業の成功物語ではない。これは、半導体製造におけるTSMCとSamsungの複占体制に、信頼できる第三の選択肢が登場する可能性を示すものだ。

この技術的同等性の達成は、地政学的な観点からも極めて重要である。最先端半導体の生産が台湾に極度に集中している現状は、世界のサプライチェーンにおける大きな脆弱性となっている。日本に拠点を置くRapidusが本格的な選択肢となれば、このリスクを分散させ、経済安全保障を強化することに繋がる。

もちろん、Rapidusの前途は平坦ではない。量産における歩留まりの安定化、巨大な投資の継続、そして何よりも顧客からの信頼獲得という高いハードルが待ち受けている。しかし、今回の技術的マイルストーンは、日本の半導体産業が再び世界のトップランナーに返り咲くための、力強い狼煙であることは間違いない。我々は今、半導体業界の新たな競争時代の幕開けを目の当たりにしているのかもしれない。

Sources