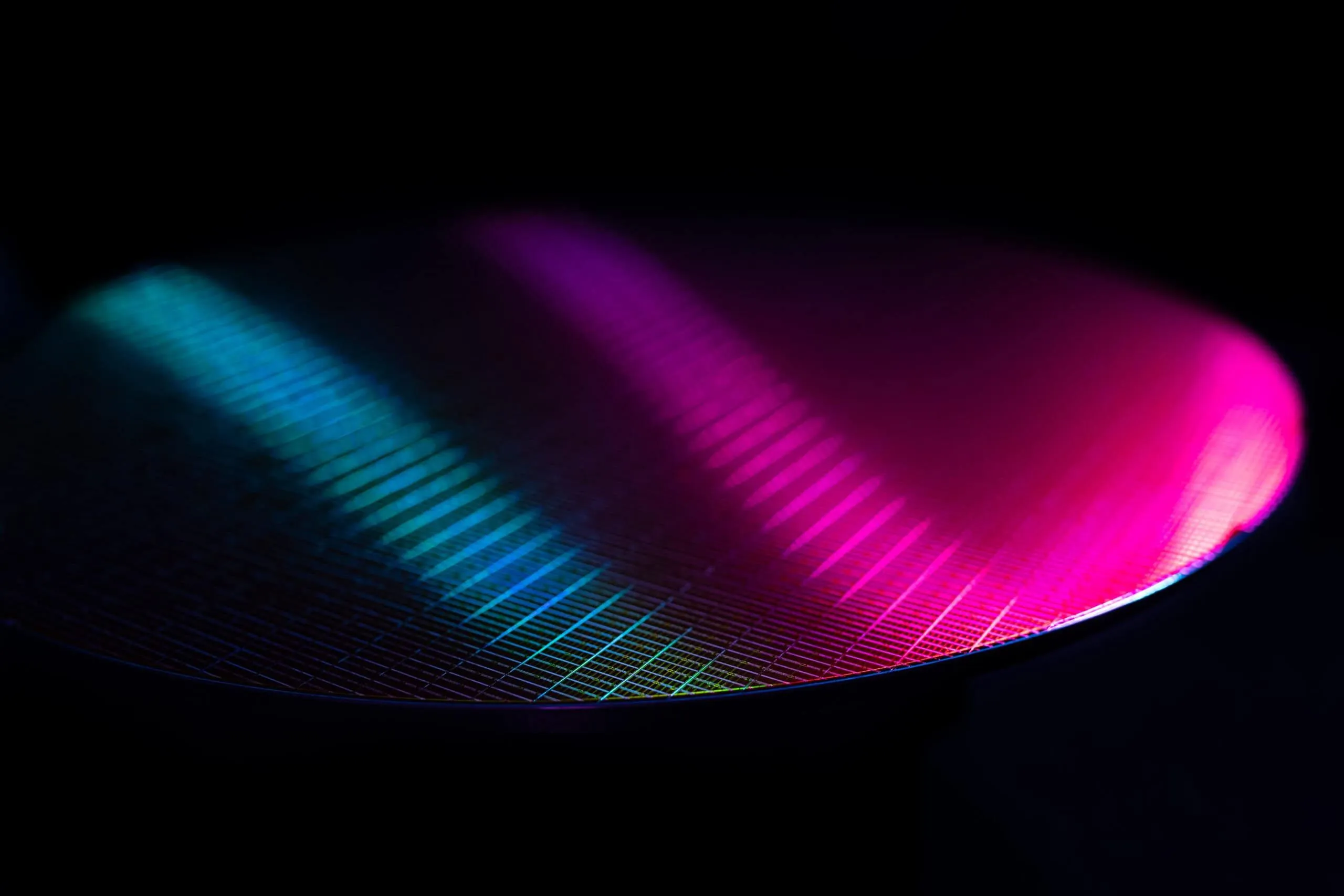

imecとゲント大学の研究チームが、3D DRAM実現に向けた極めて重要なマイルストーンを達成した。シリコン(Si)とシリコンゲルマニウム(SiGe)を120層交互に積層した超格子構造を、300mmウェハー上に欠陥なく形成することに成功したのだ。これは原子レベルの格子歪みを精密に制御し、次世代メモリの構造的基盤を確立した、半導体物理学の勝利と言える成果だ。

プレーナ型DRAMを脅かす「微細化の壁」

現代のデジタル社会を支えるDRAM(Dynamic Random Access Memory)は、これまでプレーナ型、すなわち2次元平面上での微細化によって性能と密度を向上させてきた。しかし、その微細化も物理的限界に近づいている。セルトランジスタとキャパシタのサイズを縮小し続けることは、リーク電流の増大や、十分な静電容量の確保を困難にし、信頼性の低下を招く。

この課題に対する究極的な解が、NANDフラッシュメモリで既に主流となっている3D(三次元)化である。メモリセルを垂直方向に積み上げることで、チップの占有面積を増やすことなく、記憶密度を飛躍的に向上させることができる。Samsung Electronicsが既にロードマップに掲載し、専用の研究開発施設を立ち上げるなど、業界の期待は大きい。 しかし、DRAMの3D化は、NANDのそれとは比較にならないほどの技術的障壁が存在する。

格子不整合という原子レベルの挑戦

今回の研究成果の核心は、SiとSiGeのヘテロエピタキシャル成長における「格子不整合」という根源的な課題を克服した点にある。これは、原子レベルの精緻な建築工学に他ならない。

なぜSi/SiGe構造なのか?

3D DRAMの製造プロセスでは、まずSiとSiGeを交互に積層した多層膜を形成する。その後、SiGe層のみを選択的に除去(エッチング)し、空洞を作る。この空洞にゲート絶縁膜や電極材料を充填し、GAA(Gate-All-Around)構造のトランジスタを形成する。つまり、SiGeは後の工程で除去される「犠牲層」としての役割を担い、Si層がトランジスタのチャネルとなる。このプロセスを成功させるには、原子レベルで平滑かつ急峻な界面を持つ、高品質な多層膜の形成が絶対条件となる。

ミスフィット転位:性能を破壊する結晶欠陥

しかし、ここに最大の難関が存在する。SiとSiGeでは、結晶格子を構成する原子間の距離(格子定数)が約4.2%異なる(純粋なGeの場合)。このため、Si基板上にSiGe層を成長させると、SiGe層の原子はSiの格子に合わせようと圧縮され、内部に「歪み」が蓄積する。

これは、わずかにサイズの異なるカードを精密に積み重ねようとする試みに似ている。数枚であれば歪みは内部に留まるが、積層数が増えるにつれてエネルギーが蓄積し、ある臨界点を超えると構造そのものが破綻する。半導体結晶では、この破綻が「ミスフィット転位(Misfit Dislocation)」と呼ばれる線状の結晶欠陥として現れる。一度この欠陥が発生すると、それが上層へと伝播し、デバイスの電気的特性を著しく劣化させるため、メモリチップとしては致命的だ。

“Epitaxially grown Si/Si1−xGex multi-stacks with ≥100 bilayers (≥200 sublayers) are being considered for three dimensionally vertically stacked dynamic random access memory devices. Because of the lattice mismatch between Si1−xGex and Si, the high total layer thickness, and the need for sharp interfaces, it is challenging to develop a low cost epitaxial growth process.”

「エピタキシャル成長によるSi/Si₁₋_xGex多層構造(≥100層、≥200サブ層)は、三次元垂直積層型ダイナミックランダムアクセスメモリ(DRAM)デバイスへの応用が検討されています。Si1−xGexとSiの格子不一致、高い総層厚さ、および鋭い界面の必要性により、低コストのエピタキシャル成長プロセスを開発することは困難です。」

Journal of Applied Physics, 138, 055702, 2025

今回の研究では、{65nm厚のSi}と{10nm厚のSi0.8Ge0.2}のペアを120回、合計241層もの薄膜を積層した。 SiGe層の総厚は1.2µmに達し、これは理論的な臨界膜厚を遥かに超える。にもかかわらず、ウェハーの中央部ではミスフィット転位が全く観察されず、SiGe層は完全に歪んだまま(fully strained)の状態で積層されていることが確認された。 これは、エピタキシャル成長中の温度、圧力、ガス流量といったパラメータを極限まで最適化することで、結晶欠陥の核となるエネルギー障壁を原子が乗り越えられないように精密に制御した結果である。

製造プロセスにおける課題と解決策

この偉業は、製造プロセスレベルでの複数の課題を克服して初めて可能となった。

課題1:ウェハー端部での転位発生

ウェハー中央部では完璧な結晶性が得られた一方で、ウェハーの端部(エッジ)ではミスフィット転位の発生が確認された。 これは、ウェハーの端では歪みを緩和するために必要なエネルギーが中央部より低いため、物理的に欠陥が形成されやすい領域であることに起因する。実用化には、ウェハー全面でこの転位を抑制する技術が不可欠となる。研究チームは、これを解決するアプローチとして以下の2つを提示している。

- SiGe層のGe濃度を低減する: Geの比率を20%から下げることで、Siとの格子定数差を縮小し、歪みエネルギーそのものを低減する。ただし、これは後のエッチング工程での選択比(Siを傷つけずにSiGeだけを除去する性能)とのトレードオフになる。

- SiGe層に炭素(C)を添加する: 炭素原子はシリコン原子より小さいため、SiGe格子に微量の炭素を添加することで格子定数を補償的に縮小させ、Siとの整合性を高めることができる。

課題2:積層方向および面内方向の均一性

120層もの積層を行うと、下層と上層で膜厚が微妙に変化するという問題も明らかになった。論文では、成長プロセス中に反応容器(石英管)の内壁に副生成物が堆積し、それが熱の伝わり方を変え、結果として成長速度に影響を与えた可能性を指摘している。

この問題に対し、研究チームは石英管の温度制御を改善した新しい成膜装置を用いることで、積層方向の膜厚ばらつき(Vertical uniformity)とウェハー面内の膜厚ばらつき(Lateral uniformity)の両方を大幅に改善できることを実証した。 これは、量産化を見据えた極めて重要な成果と言える。

3D DRAMのインパクト

この技術的ブレークスルーがもたらす影響は、単なるメモリの大容量化に留まらない。

まず、ロジックとメモリの物理的な距離が劇的に短縮される可能性がある。現在のコンピュータアーキテクチャでは、CPUとDRAMはマザーボード上で物理的に離れており、両者を結ぶ配線がデータ転送のボトルネックとなっている。3D DRAMは、将来的にロジックチップ上に直接メモリセルをモノリシックに積層する道を開く。これにより、TSV(貫通シリコンビア)などを介して超広帯域な接続が実現され、現在のHBM(High Bandwidth Memory)をも凌駕するメモリ帯域が期待できる。

このアーキテクチャ変革は、特にAI分野に絶大な影響を与えるだろう。大規模言語モデル(LLM)の性能は、モデルのパラメータ数と、それを処理するメモリ帯域に強く依存する。現在のGPUは、巨大なモデルを処理するために複数のチップにまたがってデータを保持し、チップ間通信のレイテンシが性能の足枷となっている。もしGPUのロジックダイ上に超高密度・超広帯域の3D DRAMを直接集積できれば、単一チップで扱えるモデルサイズが飛躍的に増大し、「メモリの壁」を打ち破るブレークスルーとなる可能性がある。

このimecの成果は、3D DRAMという未来のテクノロジーが、もはや単なる構想ではなく、現実的な工学技術の射程内に入ったことを明確に示すものだ。原子レベルの張力から秩序を工学的に創り出すこの挑戦は、半導体技術の新たな地平を切り拓き、来るべきAI時代のコンピューティング基盤を再定義する力を持っている。

Sources