半導体業界の巨人たちが覇を競うGPU市場に、カリフォルニアのスタートアップBolt Graphicsが「Zeus」という名の挑戦状を叩きつけた。2026年の開発キット提供を目指すこのGPUは、AIアクセラレータ化の潮流に背を向け、リアルタイムパストレーシングとHPC(高性能計算)における性能を追求する。そのアーキテクチャは、拡張可能メモリやRISC-V採用など、既存の常識を覆す野心的な仕様に満ちている。

GPU市場の常識に挑む異端児の設計思想

現在のGPU市場は、NVIDIAのCUDAエコシステムを筆頭に、AI/MLワークロードへの最適化が至上命題となっている。低精度演算(FP16/INT8)性能を極限まで高めるアーキテクチャが主流だ。しかし、Bolt GraphicsのZeusは、この流れとは明確に一線を画す。彼らがターゲットとするのは、物理的に正確な光の挙動を追跡するパストレーシングや、倍精度浮動小数点(FP64)演算が不可欠な科学技術計算、CADといった分野である。

この選択は、ニッチ市場を狙う戦略であると同時に、現在のGPUアーキテクチャが切り捨ててきた領域にこそ商機があるという強い信念の表れだろう。Zeusはチップレット設計を採用し、1チップの「Zeus 1c」、2チップの「Zeus 2c」、4チップの「Zeus 4c」というスケーラブルな構成を採る。だが、その真の価値は、内部のアーキテクチャと他に類を見ない機能にこそ隠されている。

Zeusアーキテクチャの革新性と合理性

Zeusの仕様書を読み解くと、単なるスペックの向上ではない、GPUアーキテクチャそのものへの問い直しが見えてくる。特に注目すべきは「RISC-V採用」「拡張可能メモリ」「ネイティブネットワーク統合」の三点だ。

RISC-V採用によるコンピュート中心設計

Zeusは、プロセッサコアの命令セットアーキテクチャ(ISA)として、オープンソースのRISC-Vを採用している。これは、x86やARM、あるいはNVIDIAやAMDの独自ISAとも異なる選択であり、極めて重要な意味を持つ。RISC-Vの採用は、ライセンス費用からの解放と、命令レベルでの自由なカスタマイズを可能にする。

一部の情報では、Zeusは従来のGPUが備えるテクスチャユニット(TMU)やラスタライザ(ROP)といったグラフィックス専用の固定機能ハードウェアを持たない可能性が示唆されている。これが事実であれば、Zeusはグラフィックスパイプラインすら汎用コンピュートコアで処理する、純粋なコンピュートアクセラレータに近い思想で設計されていることになる。Zeusの設計は、パストレーシングやHPCといった特定の計算パターンにリソースを全集中させるための、大胆かつ合理的な選択と言えるだろう。

業界の常識を覆す「拡張可能メモリ」

現代のハイエンドGPUの性能は、高帯域幅メモリ(HBM)の搭載量と帯域に大きく依存している。しかしHBMは非常に高コストであり、搭載容量にも制約がある。Zeusはこの課題に対し、驚くべき解決策を提示した。「拡張可能メモリ」である。

- ハイブリッド構成: カードには高速なLPDDR5Xメモリがオンボードで実装され、低レイテンシのアクセスを担保する。これに加え、ユーザーが増設可能なDDR5 SODIMMスロットを備える。

- 圧倒的な容量: これにより、PCIeカード単体で最大384GB、サーバー構成では最大2.25TBという、従来のGPUでは考えられないメモリ容量を実現する。

このアーキテクチャは、HPCや大規模な映像レンダリングシーンのように、メモリ階層の局所性を活かしつつ、とにかく広大なメモリ空間を必要とするアプリケーションにとって福音となり得る。メモリコントローラがオンボードLPDDR5Xと拡張DDR5間のデータ転送をいかに効率的に管理できるかが、実効性能を左右する最大の鍵となるだろう。

GPUネイティブの高速ネットワーク統合

Zeusのもう一つの革新は、GPU自体に400/800GbEのQSFP-DDポートをネイティブで統合した点にある。通常、マルチGPUクラスタでは、各GPUがPCIe経由でホストCPUに接続され、さらにNIC(ネットワークインターフェースカード)を介して外部ネットワークに接続される。

Zeusの設計は、このNICをバイパスし、GPU同士が直接高速イーサネットで通信することを可能にする。これは、AMDのInfinity FabricやNVIDIAのNVLink/NVLink Switchとは似て非なるアプローチだ。特定ベンダーのプロプライエタリなインターコネクトではなく、標準的なイーサネットを用いることで、よりオープンでコスト効率の高い大規模クラスタの構築を可能にする狙いが見える。レイテンシとシステム全体の複雑性を劇的に削減できる可能性を秘めている。

性能主張の妥当性と「シリコン前」の現実

Bolt Graphicsが公表している性能値は、まさに驚異的だ。しかし、これらは「pre-Silicon benchmarks in emulation」、すなわち実際のシリコンが製造される前のエミュレーション環境での測定値である点に、最大限の注意を払わねばならない。

FP64とパストレーシング性能:その驚異的な数値の裏側

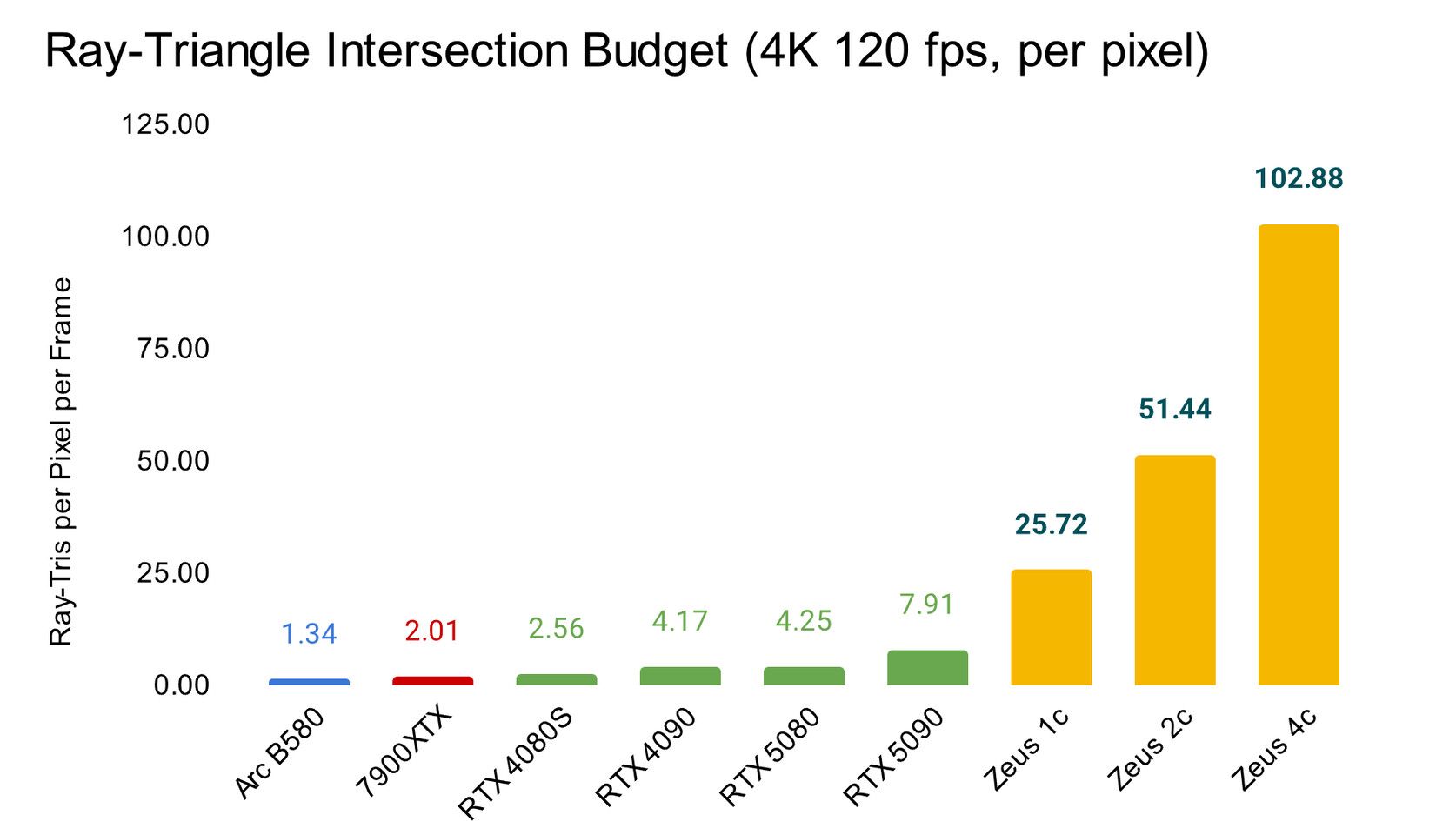

- FP64性能: 最上位のZeus 4cモデルは、NVIDIA RTX 5090の12倍のFP64性能を謳う。これは、科学技術計算分野における既存の勢力図を塗り替えかねない数値だ。

- パストレーシング: エントリーモデルのZeus 1cですら、RTX 5090を上回るパストレーシング性能(77 Gigarays/s vs 32 Gigarays/s)を持つとされる。

- 電力効率: これだけの性能を、Zeus 1cモデルはわずか120WのTDPで実現するという。

実際のところ、明らかにされているこの性能/電力比はにわかには信じがたい。エミュレーションは、チップレット間通信のレイテンシ、メモリコントローラの競合、熱や電力供給の物理的制約といった、現実世界のボトルネックを理想的に扱いがちだ。実際のシリコンでは、これらの要因によって公称値から性能が低下するのが常である。この主張は、Zeusが極めて限定的なワークロードで理想的に動作した場合の理論値に近いと考えるのが妥当だろう。

市場への影響と成功への茨の道

仮にZeusが公称値の7割程度の性能を実シリコンで達成できたとしても、そのインパクトは大きい。特に、FP64性能や大容量メモリを渇望するHPC、VFX、CAD業界では、NVIDIAの独占状態に風穴を開ける有力な選択肢となり得る。

しかし、ハードウェアの性能だけで戦えるほどGPU市場は甘くない。最大の障壁は、ソフトウェアエコシステムの不在だ。開発者が使いこなせないハードウェアはただのシリコンの塊に過ぎない。

Bolt Graphicsは、コンパイラ(LLVMバックエンドなど)、デバッガ、プロファイラ、そしてBlender、Houdini、ANSYS、Abaqusといった主要なサードパーティ製アプリケーションとの連携をいかに迅速に構築できるかに、その成否がかかっている。2026年に開発キットが登場する頃には、NVIDIAやAMDは次々世代の製品を市場に投入しているだろう。その時、Zeusが性能的優位性と、開発者を惹きつけるだけのソフトウェア基盤を両立できているか。その一点が、この野心的な挑戦の行方を占う試金石となる。

Sources