日本のVLSIシンポジウムで、Intelが自社の未来を賭けた次世代プロセス「Intel 18A」のベールを脱いだ。この壇上で同社は、現行のIntel 3プロセスと比較して、同じ消費電力で最大25%の性能向上、あるいは同じ性能を維持したまま消費電力を最大38%も削減できると言う、その大いに期待ができる性能を誇示する発表を行った。この技術は、2025年後半に量産が開始され、次世代CPU「Panther Lake」に初めて搭載される予定だ。この飛躍は、Intelの反撃の狼煙となるのか。しかし、その輝かしい数値の裏には、慎重に読み解くべき「ただし書き」も存在するようだ。

VLSIシンポジウムで明かされた18Aの衝撃的な性能

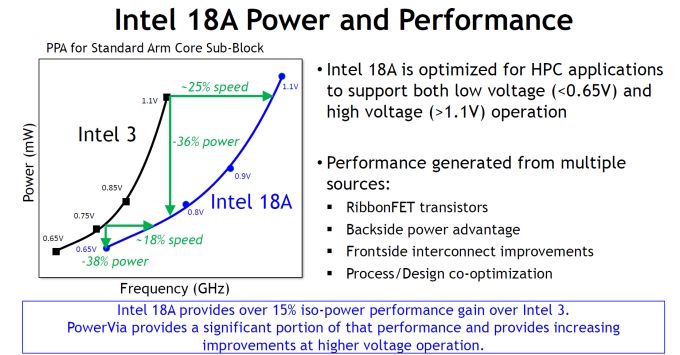

今回Intelが公開したデータは、半導体技術の進歩を測る重要な指標であるPPA(Power, Performance, Area)に関するものだ。発表は、特定のArmコアをテストチップとして用いて行われた。これは、自社アーキテクチャに依存しない客観的なプロセス性能を示すための業界標準的な手法である。

その内容は実に野心的だ。

- 高パフォーマンス動作時(高電圧 1.1V):

- 同一消費電力で、クロック周波数が最大25%向上。

- あるいは、同一クロック周波数で、消費電力を36%削減。

- 高効率動作時(低電圧 0.75V / 0.65V):

- 同一消費電力で、性能が18%向上。

- あるいは、同一性能で、消費電力を最大38%(ソースによっては40%近く)削減。

これらの数値が意味するところは大きい。例えば、デスクトップPCや高性能ノートPCでは、同じ電力枠の中でより高い処理能力を発揮できるようになり、ゲーミングやクリエイティブ作業がさらに快適になるだろう。一方で、薄型軽量ノートPCにとっては、バッテリー駆動時間の大幅な向上が期待できる。38%という電力削減は、単純計算でPCを一日中充電なしで使える未来を現実のものにするポテンシャルを秘めている。

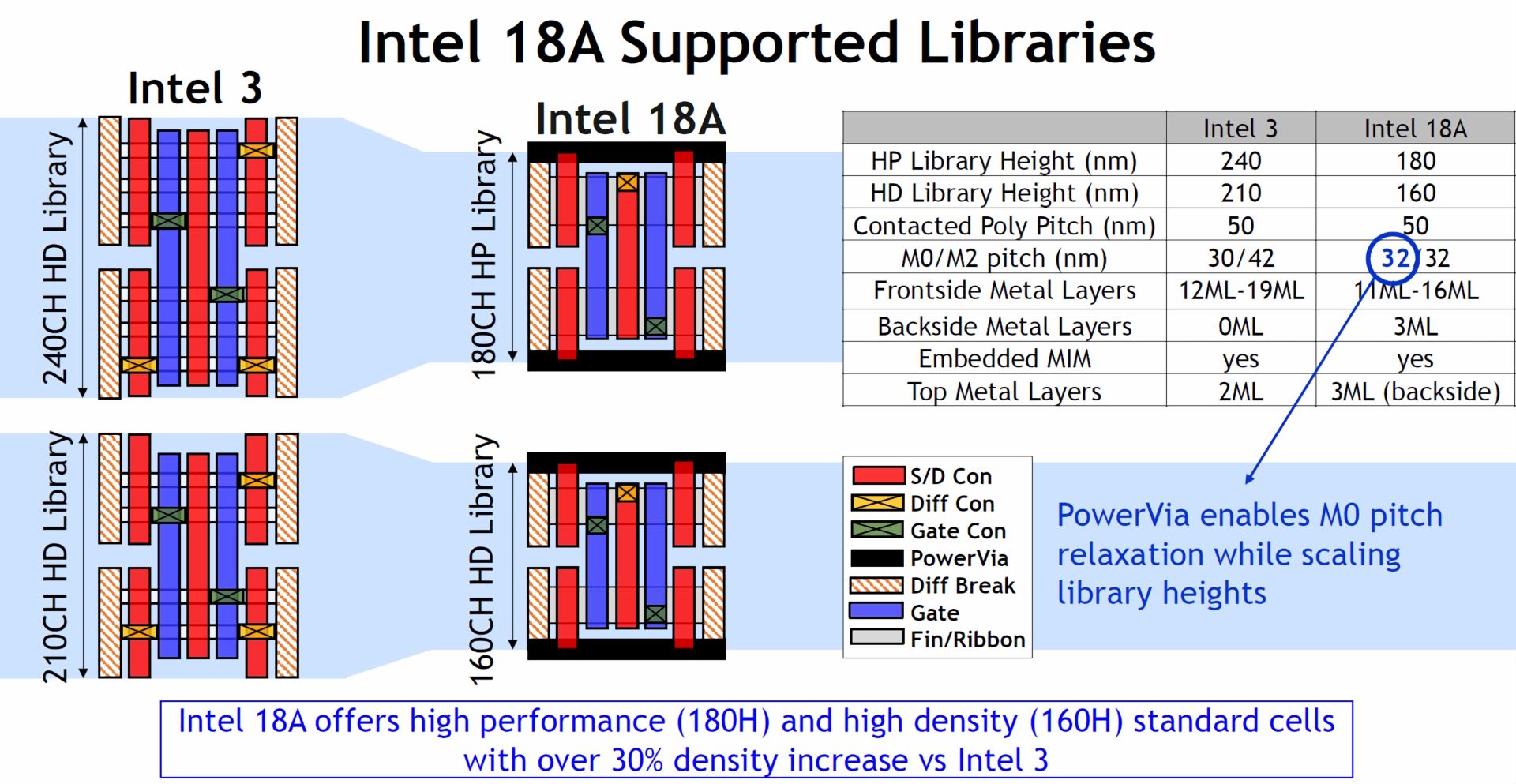

また、セルの高さが大幅に削減されたことも明らかにされた。パフォーマンス・チューニングされたセルの高さは180ナノメートル、高密度設計は160ナノメートルで、いずれも従来よりも小さくなっている。

前面の金属層は、Intel 3プロセスの12~19ナノメートルから、Intel 18Aでは11~16ナノメートルに縮小され、PowerVia互換のために後面の金属層が3層追加された。

M1~M10層のピッチが60ナノメートルから32ナノメートルに下がり、最上層のピッチも下がった。M0~M4層は低NAのEUVに露光されるため、製造工程が簡素化され、必要なマスク枚数が44%削減される。

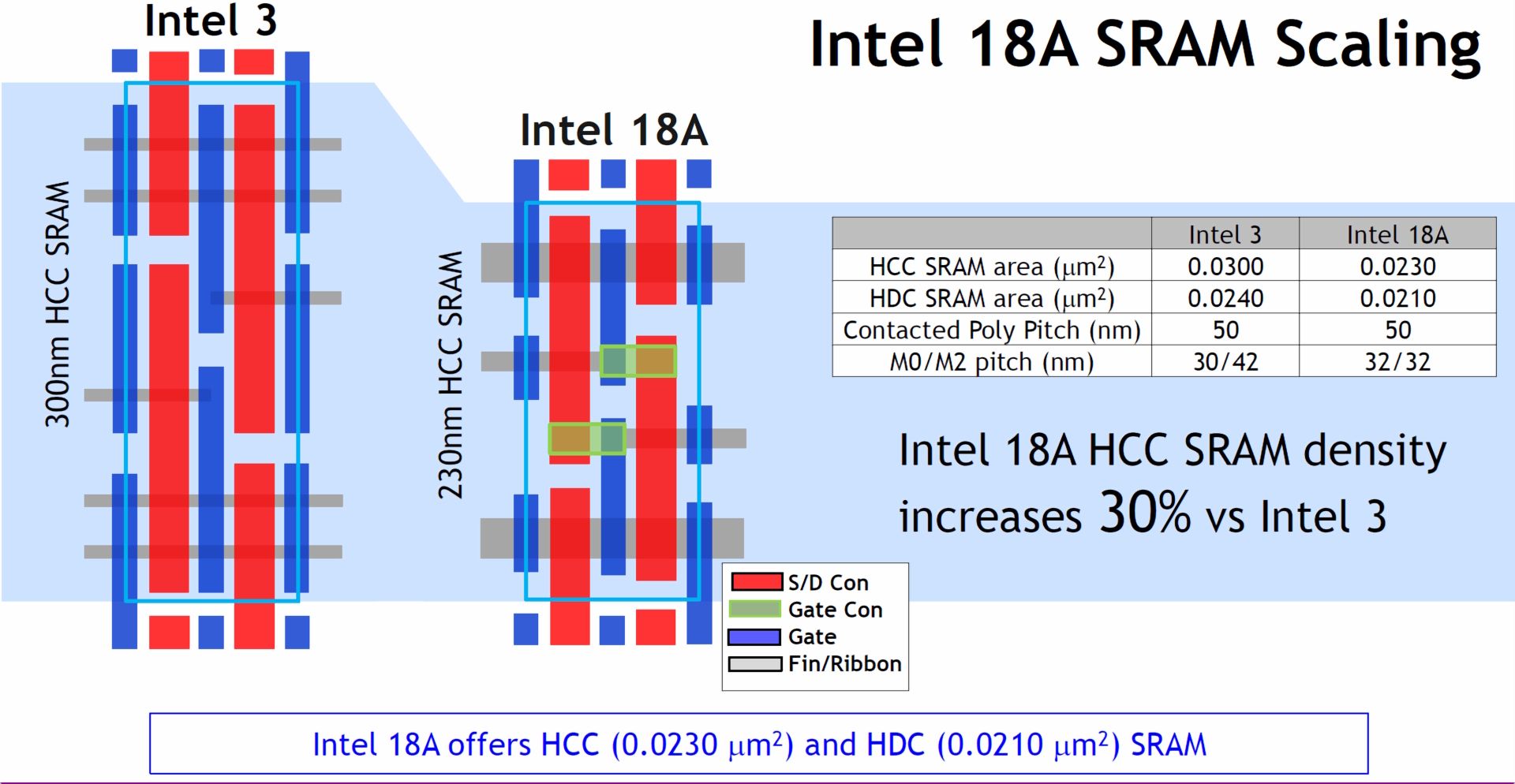

さらに、IntelはSRAM(CPUキャッシュなどに使われる高速メモリ)の密度がIntel 3比で30%向上したことも明らかにしており、チップ全体の性能向上に寄与するだろう。

成功の鍵を握る2つの革新技術:「PowerVia」と「GAAトランジスタ」

Intel 18Aの性能向上は、単なる微細化(シュリンク)によるものではない。プロセス技術の根幹に関わる2つの大きな技術革新がその原動力となっている。

1. PowerVia(裏面電力供給ネットワーク)

これは、Intelが業界に先駆けて導入する画期的な技術だ。従来、トランジスタへの電力供給線と信号線は、チップの表面(トランジスタがある側)に複雑に混在して配線されていた。これを、電力供給専用の配線網をチップの裏面(シリコンウェハーの裏側)に構築するのがPowerViaである。

道路に例えるなら、一般道(信号線)と高速道路(電力供給線)を完全に立体交差させるようなものだ。これにより、以下のメリットが生まれる。

- 配線混雑の緩和: 信号線が走る表面のスペースに余裕ができ、より効率的で高性能な配線設計が可能になる。

- 電力供給効率の向上: 電力供給経路が短く太くなるため、電圧降下(IRドロップ)が減り、トランジスタに安定したクリーンな電力を届けられる。これが性能と電力効率の向上に直結する。

- 設計と製造の簡素化: 表面の配線層を単純化できるため、設計が容易になり、製造工程も効率化される。

2. RibbonFET(GAAトランジスタ)

トランジスタ構造も、長年主流だったFinFETから、GAA(Gate-All-Around)構造である「RibbonFET」へと進化する。

FinFETでは、ゲート(電流のON/OFFを制御する部分)が半導体のチャネル(電流の通り道)を3方向から「フィン(ひれ)」のように囲んでいた。これに対しGAAでは、ゲートがチャネルをナノシート状のリボンとして4方向すべてから完全に包み込む。

水道の蛇口で言えば、FinFETが3方向からパッキンで押さえるものだとすれば、GAAは全周をパッキンで完璧に覆うようなものだ。これにより、電流のON/OFFをより精密に制御でき、OFF時のリーク電流(漏れ電流)を劇的に抑制できる。結果として、より低い電圧で安定した動作が可能となり、省電力化に大きく貢献する。

これら2大技術の相乗効果に加え、製造プロセスにおいても大きな進歩があった。露光技術にLow-NA EUV(極端紫外線)リソグラフィを最適化して用いることで、製造に必要なフォトマスクの枚数をIntel 3比で44%も削減できるという。これは製造期間の短縮とコスト削減に繋がり、Intelのファウンドリ事業(IFS)にとっても強力な武器となるはずだ。

数字の裏に潜む「ただし書き」:なぜIntel 3との比較は難しいのか?

今回の発表は手放しで賞賛できるものだが、いくつかの注意点を指摘せざるを得ない。最大のポイントは、比較対象である「Intel 3」プロセスが、コンシューマー向けのPC用CPUには一切採用されていないという事実だ。

Intel 3は、主にサーバー向けのCPU「Xeon 6」(開発コード名: Granite Rapids)で採用されているプロセスだ。一方で、Intelが直近で発表したコンシューマー向けCPU、例えば超低消費電力の「Lunar Lake」や、デスクトップ・モバイル向けの「Arrow Lake」のCPUタイル(演算部分)は、自社のIntel 3ではなく、競合であるTSMCの「N3B」プロセスで製造されている。

この事実は、いくつかの憶測を呼ぶ。Intel 3がコンシューマー製品の要求する性能や歩留まり(良品率)を満たせなかったのではないか、あるいは、TSMCを利用する方が戦略的に有利だと判断したのではないか、などだ。

いずれにせよ、我々ユーザーがPCで実際に体験したことのない「Intel 3」を基準に「25%高速化」と言われても、その真のインパクトを正確に測るのは難しい。真のライバルは、AppleのMシリーズやAMDのZenシリーズが採用するTSMCの最先端プロセスであり、最終的な評価は、18Aで製造されたPanther Lakeと、TSMCの同世代プロセスで製造された競合製品との直接対決を待たねばならない。

「4年で5世代」計画の集大成:Panther Lakeに託されたIntelの未来

今回の発表は、Pat Gelsinger CEOが2021年に就任して以来、社運を賭けて推進してきた「IDM 2.0」戦略と、その中核である「4年間で5つのプロセスノードを立ち上げる(5N4Y)」というロードマップの最終目的地を示すものだ。

Intel 7 (Alder Lake) → Intel 4 (Meteor Lake) → Intel 3 (Xeon 6) → Intel 20A → そして、Intel 18A。

この野心的な計画は、製造技術の遅れによって失われたリーダーシップを奪還するための、まさに茨の道だった。18Aはその集大成であり、PowerViaとGAAという2つの大きな技術的賭けが成功するかどうかの試金石となる。

この重要なプロセスを採用する最初のコンシューマー製品が「Panther Lake」だ。2025年後半から2026年初頭の登場が見込まれており、Intelの技術力が再び世界をリードできるかを証明する極めて重要な製品となる。さらに、サーバー市場においても、Eコア(高効率コア)のみで構成される次世代Xeon「Clearwater Forest」が18Aで製造される予定であり、データセンター市場における競争力を取り戻すための鍵を握っている。

期待と懐疑の狭間で。真価が問われる2025年

IntelがVLSIシンポジウムで示した18Aプロセスの性能指標は、間違いなく目覚ましいものだ。PowerViaとGAAトランジスタという技術的野心は、IntelのR&D能力が未だ健在であることを証明している。もしこの数値が実際の製品で再現されれば、PCの性能とバッテリー寿命は新たな次元に到達するだろう。

しかし、過去の度重なるプロセス遅延の歴史と、比較対象であるIntel 3の立ち位置の曖昧さは、我々に冷静な視点を要求する。発表された数字はあくまで「理論値」であり、本当の勝負は、Panther Lakeが市場に投入され、TSMCの牙城で戦う競合製品と真っ向からぶつかるその時まで待たなければならない。

Intelの逆襲劇は、いよいよクライマックスを迎えようとしている。2025年、半導体業界の勢力図は再び大きく塗り替えられることになるのかもしれない。

Sources