シリコンベースのCMOS技術が物理的限界に近づく中、次世代半導体の最有力候補として2次元(2D)材料への期待が高まっている。しかし、その商用化には「ゲートスタック」と呼ばれる中核部分の統合技術という高い壁が存在した。この難題に対し、ソウル国立大学(SNU)のイ・チョルホ(Chul-Ho Lee)教授率いる研究チームが、包括的な技術ロードマップを学術誌『Nature Electronics』で発表している。

シリコン時代の黄昏と2次元半導体の夜明け

現代のデジタル社会を支える半導体は、長らくシリコン(Si)を主材料とするCMOS技術の微細化によって進化してきた。トランジスタをより小さく、より高密度に集積することで、プロセッサの性能向上と低消費電力化を両立させてきたのである。しかし、その微細化もサブナノメートル領域に突入し、無視できない物理的・静電的な制約に直面している。

ゲート長が極端に短くなると、ソースからドレインへ流れる電流をゲートで完全に制御しきれなくなる「短チャネル効果」や、絶縁膜が原子レベルの薄さになることで電子が通り抜けてしまう「量子トンネル効果」によるリーク電流の増大が深刻化する。これらの問題は、性能向上を頭打ちにさせ、消費電力の増大を招く。ムーアの法則の終焉が囁かれる背景には、こうしたシリコン材料そのものの物性に根差した限界が存在する。

この閉塞感を打破する技術として、グラフェンや遷移金属ダイカルコゲナイド(TMDs)に代表される2次元材料が脚光を浴びている。これらの材料は、原子一層という究極的な薄さを持ちながら、安定した半導体特性を維持できる。この物理的な薄さは、ゲートによるチャネルの静電制御を極めて効率的に行うことを可能にし、短チャネル効果を効果的に抑制できる。Samsung、TSMC、Intel、そしてベルギーの研究機関imecといった世界の主要半導体企業・研究機関が、2030年代半ば以降のポストシリコン時代を見据え、2次元半導体を技術ロードマップに組み込み、大規模な研究開発に着手している事実は、この技術への期待の高さを物語っている。

2次元トランジスタ最大の障壁「ゲートスタック」の構造と課題

2次元半導体の優れたポテンシャルを最大限に引き出す上で、最大の技術的障壁とされているのが「ゲートスタック」の形成技術である。

ゲートスタックとは何か?トランジスタの心臓部を解剖する

トランジスタは、電流のオン・オフを切り替えるスイッチとして機能する。その心臓部がゲートスタックである。これは、電流が流れる経路である「チャネル」の上に積層された構造体で、主に「ゲート電極」と、チャネルとの間を電気的に絶縁する「ゲート絶縁膜(誘電体)」から構成される。

ゲート電極に電圧を印加すると、その電界がゲート絶縁膜を介してチャネルに作用し、キャリア(電子または正孔)をチャネルに引き寄せて電流が流れる道(導電層)を形成する(オン状態)。電圧をなくすとキャリアはチャネルからいなくなり、電流は流れなくなる(オフ状態)。このオン・オフの切り替え性能は、ゲートスタックの品質に完全に依存する。高品質なゲートスタックとは、具体的には以下の条件を満たすものを指す。

- 高品質な絶縁膜: ゲートリーク電流を最小限に抑えるため、優れた絶縁性を持つ。

- 高い静電容量: ゲート電圧の変化に対して、チャネルの電位を効率的に変調するため、より薄く、より高い誘電率(high-k)を持つ材料が求められる。

- 理想的な界面: ゲート絶縁膜とチャネル半導体との界面に、電子の動きを妨げる欠陥(界面トラップ)が極めて少ないこと。

シリコンの場合、熱酸化によって極めて高品質な絶縁膜である二酸化ケイ素(SiO2)を自己整合的に形成でき、その界面も非常に清浄に保てるという、材料科学的な奇跡に支えられてきた。しかし、この常識は2次元半導体には通用しない。

なぜ既存のSiプロセスは2次元材料に通用しないのか?

2次元材料(例えばMoS2など)の表面は、シリコンとは根本的に異なる。シリコン表面には原子の結合手がむき出しになった「ダングリングボンド」が存在し、これが酸化膜と強力な共有結合を形成する。一方、2次元材料の表面は原子的に平坦で、ダングリングボンドが存在しない。原子層内は共有結合で固く結ばれているが、層と層の間は弱いファンデルワールス(vdW)力で結合している。

この化学的に不活性な表面に、原子層堆積(ALD)のような既存の成膜プロセスを用いて絶縁膜を直接形成しようとすると、膜の核が均一に生成されず、膜質が著しく劣化する。また、無理な成膜プロセスは2次元材料の繊細な表面に物理的・化学的なダメージを与え、性能劣化の根源となる界面トラップを大量に生成してしまう。これはトランジスタの移動度低下、閾値電圧の不安定化、ヒステリシスの増大といった致命的な問題を引き起こす。2次元半導体の商用化は、この界面問題を解決する新しいゲートスタック統合技術の確立にかかっているのである。

【技術的深掘り】SNUが提示する5つのゲートスタック統合アプローチ

イ・チョルホ教授の研究チームは、この難題に対する世界中のアプローチを分析・分類し、体系的なロードマップとして提示した。彼らはゲートスタックの統合手法を以下の5つのカテゴリに大別し、それぞれの優劣を定量的に評価している。

カテゴリ1: ファンデルワールス(vdW)誘電体

これは、六方晶窒化ホウ素(h-BN)のような、それ自体が2次元層状物質である絶縁体を、メカニカルな転写技術を用いて2次元半導体チャネルの上に直接積層するアプローチである。

- アーキテクチャ的利点: 2次元材料同士を重ね合わせるため、物理的なダメージや化学反応を伴わず、欠陥の極めて少ない理想的な「vdWヘテロ界面」を形成できる。原理的には、最も優れたトランジスタ特性を引き出せる可能性がある。

- 技術的課題: 研究室レベルでは有効だが、ウェハスケールでの均一な転写や、既存の半導体製造ラインとのプロセス統合が極めて難しい。量産技術としてのスケーラビリティに大きな課題を抱える。

カテゴリ2: vdW酸化誘電体

詳細は論文で述べられているが、これはvdW材料そのものを酸化させて絶縁膜に変換する手法と考えられる。例えば、特定の2次元金属材料を堆積させた後、それを酸化させることで絶縁層を形成するアプローチなどが含まれると推察される。

- アーキテクチャ的利点: 界面をvdW材料で形成した後に絶縁膜化するため、界面の品質をある程度維持できる可能性がある。

- 技術的課題: 酸化プロセスが下地の2次元半導体に与える影響の精密な制御が必要であり、均一な酸化膜厚の確保が難しい。

カテゴリ3: 準vdW誘電体

これも詳細な定義は元情報にないが、完全な層状構造を持たないものの、表面の性質がvdW材料に近く、2次元半導体との親和性が高い絶縁材料を用いるアプローチを指すと考えられる。特定の有機材料などが候補となりうる。

- アーキテクチャ的利点: 従来の成膜プロセスと親和性のある材料を選択できれば、vdW誘電体アプローチよりもプロセス統合が容易になる可能性がある。

- 技術的課題: 材料探索が重要であり、絶縁性能と界面特性を両立する最適な材料を見つけ出す必要がある。

カテゴリ4: vdWシード誘電体

これは、量産性とのバランスを取った極めて現実的なハイブリッドアプローチである。まず2次元半導体表面に、ALD成膜の「足がかり」となる極めて薄いシード層(種層)を形成し、その上から従来のhigh-k絶縁膜を堆積させる。

- アーキテクチャ的利点: シード層が2次元半導体表面を保護するバッファとして機能し、ALDプロセスによる直接的なダメージを防ぐ。これにより、既存の成熟した成膜技術を活用しつつ、比較的良好な界面を形成できる。

- 技術的課題: シード層自体の品質、膜厚の精密な制御が鍵となる。シード層が厚すぎると、実効的な絶縁膜厚(EOT: 等価酸化膜厚)が増加し、トランジスタの性能が低下するトレードオフが存在する。

カテゴリ5: 非vdWシード誘電体

vdW物質を用いず、プラズマ処理や化学処理によって2次元半導体表面をわずかに改質し、ALD膜の成膜性を向上させるアプローチである。

- アーキテクチャ的利点: プロセスが比較的簡便であり、既存の製造装置を流用しやすい。

- 技術的課題: 表面処理は、2次元半導体チャネルに欠陥を導入するリスクと常に隣り合わせである。処理条件の最適化が極めて重要となり、性能とプロセスの安定性の間で厳しいトレードオフの管理が求められる。

IRDS目標とのベンチマーク分析

この研究の独創性は、これら5つのアプローチを単に分類しただけでなく、それぞれの性能を国際半導体技術ロードマップ(IRDS)が示す将来の性能目標と定量的に比較・評価した点にある。 具体的には、「界面トラップ密度」「等価酸化膜厚(EOT)」「ゲートリーク電流密度」「閾値電圧」「供給電圧」といった複数の重要指標(Metrics)に対して各アプローチをプロットし、目標達成度を可視化した。このベンチマーキングにより、研究者や技術者は、自身のアプローチが業界全体の目標に対してどの位置にあるのか、次に何を克服すべきなのかを客観的に把握できる。これは、学術的研究と産業界のニーズとの間のギャップを埋める、極めて価値の高い「羅針盤」と言える。

ゲートスタックの未来:強誘電体とBEOL統合への道

本研究は、さらに一歩進んで、ゲートスタック技術の将来展望にも踏み込んでいる。

強誘電体ゲートスタックが拓く新応用

ゲート絶縁膜に、ハフニウムジルコニウム酸化物(HfZrO2)のような強誘電体材料を組み込むことで、トランジスタの性能を飛躍的に向上させる可能性が示された。

- 超低消費電力ロジック: 強誘電体は、電界によって内部の分極が反転する特性を持つ。これを利用すると「負性容量」と呼ばれる効果が生じ、トランジスタのスイッチング特性(サブスレッショルドスイング)を、従来の物理限界である60mV/dec(室温)以下にまで急峻にできる。これは、より低い電圧でトランジスタをオン・オフできることを意味し、AIチップやモバイル機器における消費電力を劇的に削減する道を開く。

- 不揮発性メモリとインメモリコンピューティング: 強誘電体は、外部電界がなくても分極状態を保持できる(残留分極)。この性質を利用すれば、トランジスタ自体がデータ記憶機能を持つ不揮発性メモリ(FeFET)を実現できる。さらに、メモリと演算を同じ素子で行う「インメモリコンピューティング」アーキテクチャへの応用も期待される。これは、CPUとメモリ間のデータ移動(フォン・ノイマン・ボトルネック)を解消し、データ中心のAI処理を大幅に高速化する可能性を秘めている。

産業化への最終関門:BEOL適合性と低温プロセス

研究の最終章では、産業化に向けた極めて実践的な要件が提示されている。それが「BEOL(Back-End-of-Line)適合性」である。

半導体製造プロセスは、トランジスタ自体を作り込む前工程(FEOL)と、その上に金属配線を形成していく後工程(BEOL)に大別される。将来、3D-ICのようにトランジスタの層を垂直に積み重ねる「モノリシック3D集積」を実現するには、下の層に作り込んだトランジスタや配線を壊さないよう、上の層のトランジスタを低温で形成する必要がある。

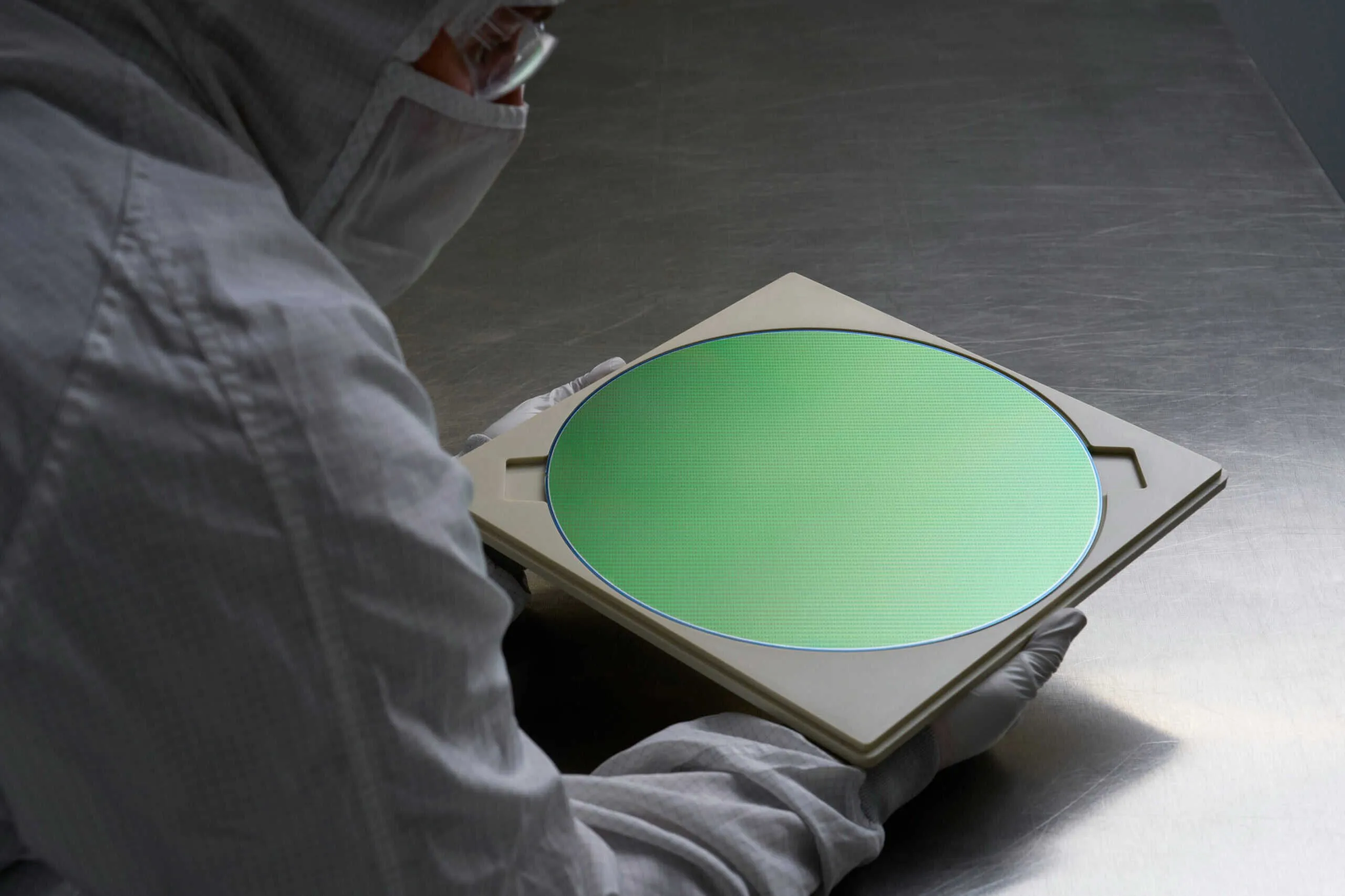

これは、2次元半導体のゲートスタック形成プロセス全体を、従来の高温プロセスではなく、配線が耐えられる400℃以下の低温で行わなければならないことを意味する。 さらに、直径300mmのウェハ全面にわたる均一性や、長期的な動作信頼性の確保も、量産化には避けて通れない課題である。この研究は、理論上の性能だけでなく、こうした製造上の制約までを考慮に入れた技術開発の方向性を示した点で、非常に現実的かつ影響力が大きい。

2次元半導体商用化への現実的な羅針盤

ソウル国立大学の研究チームによるこの成果は、単なる新しいゲートスタック技術の報告ではない。乱立していた個別技術を体系的に整理し、共通の性能指標と業界目標(IRDS)に照らして評価し、将来の応用と量産化の課題までを見据えた、初の包括的な「標準設計図」を提示した点に最大の意義がある。

2次元半導体という有望な技術が、研究室の基礎研究から産業界における大規模生産へと移行するためには、このような学術界と産業界の双方にとっての共通言語となるロードマップが不可欠である。本研究は、ポストシリコン時代の半導体開発を加速させる、極めて重要なマイルストーンとなるだろう。今後、このロードマップを基盤とした産学連携が加速し、デバイスレベルでの統合と実用化に向けた研究が飛躍的に進展することが期待される。

論文

- Nature Electronics: Gate stack engineering of two-dimensional transistors

参考文献