IntelはFoundry Direct Connect 2025イベントにおいて、ファウンドリ事業の最新ロードマップと戦略を発表した。新CEO Lip-Bu Tan氏が登壇し、次世代プロセス「Intel 14A」への取り組み開始や、今後主力となる「Intel 18A」の高性能版および業界注目の3Dダイ積層対応版の投入計画を明らかにした。さらに、先進パッケージング技術の拡充やエコシステムパートナーとの連携強化も発表され、半導体製造受託分野におけるリーダーシップ奪還への強い意志を示した形である。

Intel Foundry Direct Connect 2025:主要発表ハイライト

サンノゼで開催されたIntel Foundry Direct Connect 2025は、Intelのファウンドリ事業における重要なマイルストーンとなるイベントであった。新CEOのLip-Bu Tan氏は、顧客の声に耳を傾け、信頼を勝ち取ることを最優先事項とし、「サービスファースト」の企業文化への転換を強調した。

主な発表内容は以下の通りである。

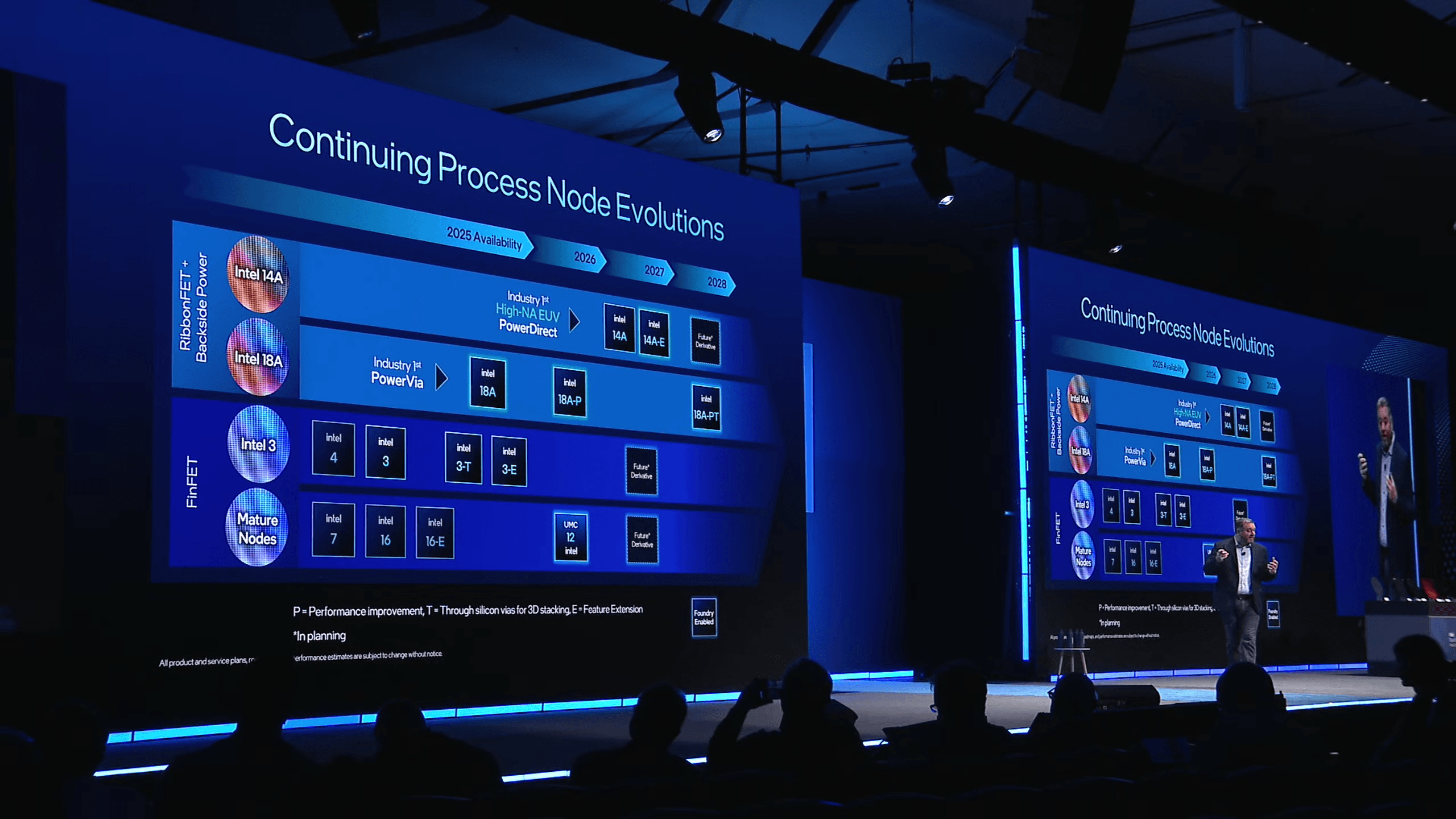

- Intel 14Aプロセス: 次世代1.4nm相当プロセス「Intel 14A」の主要顧客へのエンゲージメント開始と早期PDK(Process Design Kit)提供。改良型裏面電源供給(BSPDN)技術「PowerDirect」を採用。

- Intel 18Aとその派生:

- 18A(1.8nm相当)のリスク生産開始、年内量産予定。

- 高性能版「18A-P」の初期ウェハー製造開始。

- 3Dダイ積層対応版「18A-PT」の開発発表。Foveros Directハイブリッドボンディング技術を採用。

- 成熟プロセス: Intel 16nmの最初の量産テープアウト完了、UMCと共同開発中の12nmの顧客エンゲージメント開始。

- 先進パッケージング: EMIB-T(TSV追加)、Foveros-R/B(コスト効率向上)、Foveros Direct(3D積層)などの新技術発表。Amkorとの提携によるエコシステム拡大。

- エコシステム強化: 新たな「Intel Foundry Chiplet Alliance」および「Value Chain Alliance」プログラムの設立。Synopsys、Cadence、Siemens EDA、PDF Solutionsなど主要パートナーとの連携深化。

- 製造拠点: アリゾナFab 52での18Aウェハ処理成功。グローバルな製造・研究開発体制(米国、イスラエル、アイルランド、マレーシアなど)の強化。

これらの発表は、Intelが単なるチップメーカーから、顧客の多様なニーズに応える「システムファウンドリ」へと変貌を遂げようとしていることを示している。

プロセス技術ロードマップ詳報:14Aから成熟ノードまで

Intel Foundryの技術ロードマップは、最先端ノードから成熟ノードまで多岐にわたる。特に注目されるのは、次世代の「オングストローム時代」を担うIntel 14Aと、現行主力となる18Aの進化である。

Intel 14A:High-NA EUVとPowerDirectで次世代へ

Intel 18Aの後継となるIntel 14A(1.4nm相当)は、Intel Foundryの次世代フラッグシッププロセスである。すでに主要顧客へのエンゲージメントが開始され、早期版PDKが提供されており、複数の顧客がテストチップの製造計画を進めている。

14Aの最大の特徴の一つは、Intel 18Aで導入された裏面電源供給技術(BSPDN)「PowerVia」を進化させた「PowerDirect」の採用である。PowerDirectは、トランジスタのソースとドレインに専用コンタクトを通じて直接電力を供給する方式で、抵抗を最小限に抑え、電力効率を最大化することを目指す。これは、トランジスタのコンタクト層にナノTSV(Through-Silicon Via)で接続する現行のPowerViaよりも、さらに直接的で効率的な接続方式となる。競合のTSMCは、2026年後半に生産開始予定のA16ノードで「Super Power Rail (SPR)」と呼ばれる直接コンタクト型のBSPDNを導入する計画だが、14Aはこの分野で先行することを目指しており、IntelはTSMCに対してBSPDNで2世代先行する可能性があると指摘している。

また、14Aは業界で初めてHigh-NA(高開口数)EUV(極端紫外線)リソグラフィ技術を量産に採用する可能性があるプロセスとしても注目されている。High-NA EUVは、従来のEUVよりもさらに微細な回路パターン形成を可能にする次世代技術だ。ただし、Intelは現時点でHigh-NA EUVと従来のLow-NA EUVのどちらを採用するか、あるいは併用するかの最終決定はしておらず、設計ルール上はどちらにも対応可能であり、顧客への影響はないとしている。Naga Chandrasekaran氏(Intel Foundry CTO兼COO)は、「High-NA EUVは期待通りに機能しており、適切なタイミングで導入する」と述べている。一方、TSMCは2028年頃に登場予定の競合A14ノードではHigh-NA EUVを採用しない方針を示している。

Intelは14Aについて、18Aでの学びを活かし、より予測可能な実行を顧客に約束している。ワットあたり性能で15-20%の向上、チップ密度で約30%の向上、消費電力で25%以上の削減を見込んでいる。

Intel 18Aとその派生:リスク生産開始と3D積層への道

Intel 18A(1.8nm相当)は、Intelがプロセス技術でリーダーシップを取り戻す上で極めて重要なノードだ。業界で初めてRibbonFET(GAA:Gate-All-Aroundトランジスタの一種)とPowerVia(裏面電源供給ネットワーク:BSPDN)の両方を採用したプロセスとして注目されている。

最新情報として、18Aはリスク生産(初期の少量生産)段階に入り、2025年後半にはHVM(High Volume Manufacturing:大量生産)が開始される予定とのことだ。最初の量産はオレゴンの工場で行われるが、アリゾナのFab 52でも最初のウェハーロット処理が完了しており、アリゾナでの生産開始も近いことを示唆している。このスケジュールは、年末登場が噂されるコンシューマ向けCPU「Panther Lake」などの製品投入時期とも符合する。Naga Chandrasekaran氏は、18Aの欠陥密度は計画通りに改善しており、最高のウェハーはすでに目標を達成、将来の量産向けウェハーも良好な進捗を示していると述べ、2025年後半の量産開始に自信を見せた。

競合であるTSMCのN2(2nm相当)プロセスも18Aとほぼ同時期にHVM開始が見込まれている。N2はGAAトランジスタを採用するが、BSPDNは採用しない。初期の比較では、18Aは速度と電力効率で優位に立つ可能性がある一方、TSMCは密度(とおそらくコスト)で優位性を保つと見られているが、実装によって差が出る可能性もある。

Intelは18Aのラインナップを拡充し、顧客の多様なニーズに応える戦略を打ち出している。

- 18A-P (Performance): 18Aの高性能版として開発が進んでおり、すでに初期ウェハーが製造ラインを流れている。電力と周波数のカーブを最適化し、ワットあたり性能を5-10%向上させる。より低い電圧での特性も改善し、汎用CPU以外の用途にも対応しやすくなる。18Aと設計ルール互換性があるため、既存設計の移行が容易である。

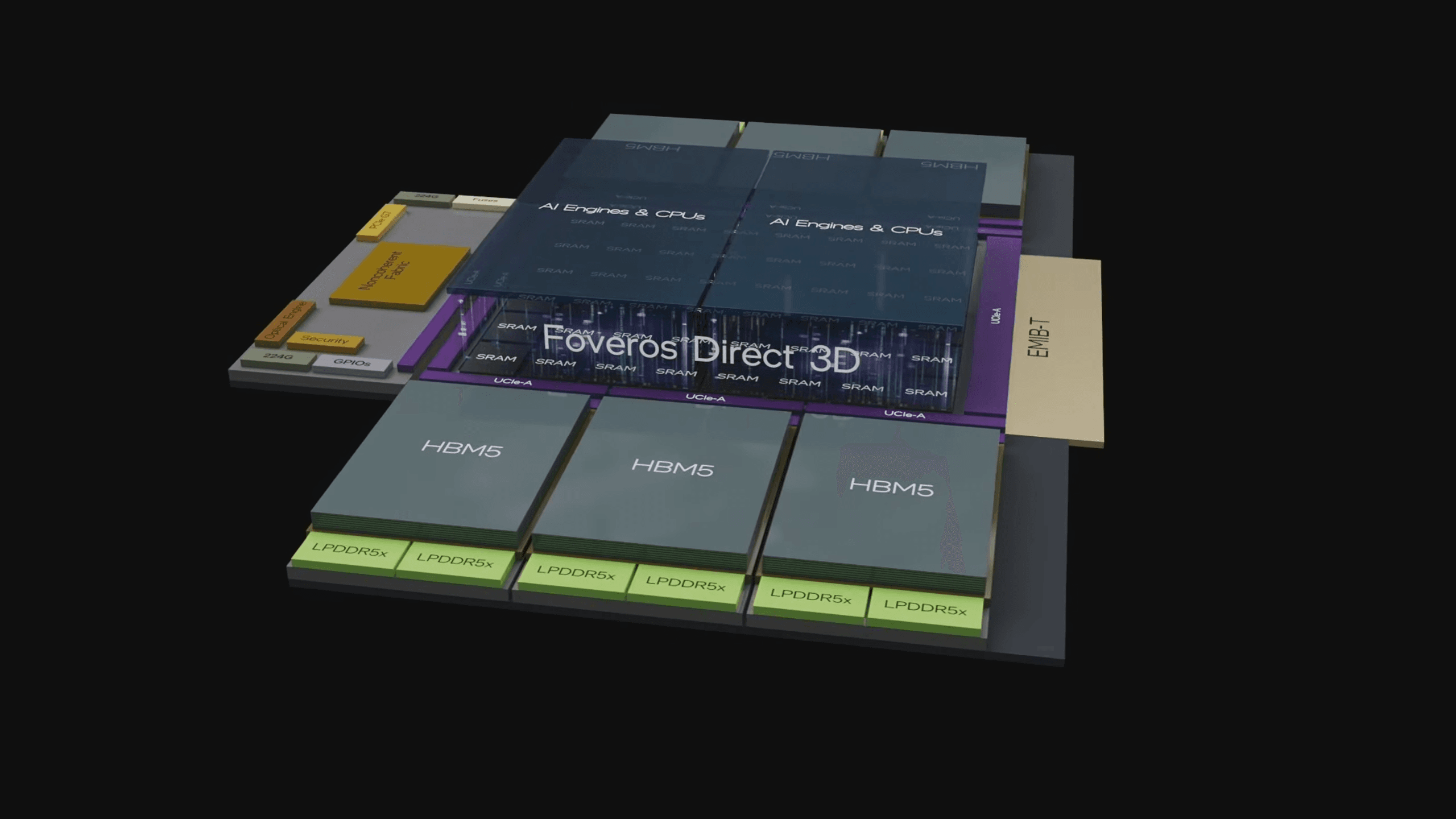

- 18A-PT (Performance + TSV/3D): 今回新たに発表された最も注目すべき派生版の一つだ。18A-Pの性能・効率向上に加え、Foveros Directによる3Dハイブリッドボンディング技術に対応する。これは、マイクロバンプやはんだを使わず、TSV(シリコン貫通ビア)を介して銅(Cu)同士を直接接合する先進的なダイ積層技術である。Intelの実装では、接続間隔(ピッチ)を5マイクロメートル(µm)未満とし、当初目標の10µmから大幅に高密度化する計画である。

この18A-PTの発表は非常に重要だ。なぜなら、TSMCはすでに「SoIC-X」と呼ばれる同様のハイブリッドボンディング技術を実用化しており、AMDの3D V-Cache搭載Ryzen X3Dプロセッサなどで採用されているからだ。TSMCのSoIC-Xの現行ピッチは4.5~9µm(AMD X3Dは9µm)であり、Intelの5µm未満という目標が達成されれば、積層密度でTSMCに匹敵、あるいは凌駕する可能性が出てくる。これにより、Intel自身やファウンドリ顧客が、例えば大容量キャッシュメモリをCPUダイ上に積層するといった、より高性能で高密度なチップ設計を実現できるようになる。IntelのXeon CPU「Clearwater Forest」はFoveros Directを採用する最初の製品の一つだが、ベースダイはIntel 3-Tであり、その上に18Aのコンピュートダイが積層される。18A-PTによって、18Aダイ自体がベースとなり、その上にさらに別のダイ(SRAMキャッシュなど)を積層することが可能になる。Kevin O’Buckley氏(Intel Foundry SVP兼GM)は、18A-PTが次世代のHPC、AI、エッジアプリケーション向けベースダイとして最適であり、IPや設計ブロックの再利用も容易だと述べている。

成熟プロセス:Intel 16と12nmも着実に前進

最先端だけでなく、成熟プロセスの提供もファウンドリ事業の重要な柱だ。

- Intel 16: Intelの22FFLノードをベースに、業界標準の設計ツールやPDKに対応させたプロセス。最初の量産テープアウト(設計完了し製造に移行すること)が完了し、現在製造中である。アイルランド工場などで生産されている。MediaTekが最初の顧客であり、ゼロから量産に至る最初の製品で成功を収めたと発表している。

- Intel 12nm: 台湾のファウンドリUMCとの提携により開発が進められている。2027年からアリゾナの3つの工場で生産開始予定。主にモバイル、通信インフラ、ネットワーク用途向け。すでに主要顧客とのエンゲージメントが始まっている。UMCのMing Sung氏もビデオメッセージで協力の進展を強調した。

これらの成熟ノードは、既存の設備を活用しつつ、多様な市場のニーズに応える上で重要な役割を担う。

先進パッケージング技術:3D積層とエコシステム拡大が鍵

現代の半導体は、単一のシリコンチップ(モノリシックダイ)ではなく、複数のチップレットを高度に統合する「先進パッケージング」技術が性能向上の鍵を握っている。Intel Foundryはこの分野で独自の技術ポートフォリオを持ち、さらなる強化を進めている。

EMIBとFoverosの進化

Intelの主要なパッケージング技術には、2.5D(水平方向接続)のEMIB(Embedded Multi-die Interconnect Bridge)と、3D(垂直方向積層)のFoverosがある。

- EMIB (2.5D): シリコンブリッジをパッケージ基板に埋め込み、チップレット間を高密度に接続する技術。今回発表されたEMIB-Tは、従来のEMIBブリッジにTSVを追加し、電力供給と信号伝送能力を向上させる。これにより、次世代高帯域幅メモリ(HBM4)や高速インターフェース規格(UCIe 32Gbps)への対応を強化する。EMIBは巨大なインターポーザを必要としないため、コスト効率や製造期間短縮(週単位)のメリットがあるとされる。Intelは最大120x188mm、12倍レチクルサイズを超える巨大パッケージもEMIBで実現可能としている。

- Foveros (3D/2.5D): ダイを垂直に積層する技術。今回、コスト効率と柔軟性を高めるために、RDL(再配線層)インターポーザを用いたFoveros-Rと、RDLとシリコンブリッジを組み合わせたFoveros-Bという2つの新しい2.5D向けオプションが追加された。これらは2027年に生産準備が整う予定。そして、前述の18A-PTでも採用される3D積層技術Foveros Directは、銅(Cu)同士を直接接合するハイブリッドボンディングにより、超高帯域幅、低消費電力、高密度のダイ間接続を実現する。

これらの技術は、AIアクセラレータや高性能コンピューティング(HPC)など、複雑なヘテロジニアス(異種混載)システムオンパッケージ(SoP)の実現に不可欠である。Kevin O’Buckley氏は、顧客が求める将来の製品像として、複数のベースダイ上に多数のコンピュートダイを積層し、大量のHBMやLPDDRメモリを電気・光インターフェースで接続した、12倍レチクルサイズ超の巨大システムを提示し、Intel Foundryがこれを実現できるユニークな立場にあると強調した。

Amkorとの提携によるエコシステム拡大

これまでIntelの先進パッケージング、特にEMIBの組み立ては主にIntel内部で行われてきた。しかし、ファウンドリ顧客からは、サプライチェーンの選択肢拡大を求める声が上がっていた。

この声に応える形で、Intelは大手OSAT(Outsourced Semiconductor Assembly and Test:半導体後工程受託企業)であるAmkor Technologyとの提携を発表した。AmkorはIntelのEMIBプロセス認定を取得し、Intel社内と同等の品質・性能でEMIBパッケージングサービスを提供することを目指す。Amkor COOのKevin Angel氏は、EMIBを特にAIアプリケーション向けの魅力的な技術と評価しており、Amkorのポートフォリオへの戦略的な追加であると述べた。この提携により、顧客はIntel FoundryとAmkorのどちらでEMIBパッケージングを行うか選択できるようになり、サプライチェーンの柔軟性とリスク分散が向上する。Amkorは韓国を皮切りに、将来的には米国アリゾナの新工場(今年着工予定)でも対応する計画で、2026年末までに完全にサービス提供可能となることを目指している。

光インターコネクトへの注力

データセンターなどでのデータ転送量増大に伴い、従来の電気配線に代わる光インターコネクト技術への期待が高まっている。Intelは、チップ間あるいはパッケージ内で光接続を実現する「コアパッケージドオプティクス(CPO)」にも注力している。光インターコネクトは、帯域幅、遅延、電力効率、接続密度において電気配線を凌駕する可能性を秘めており、Intelの先進パッケージング技術と組み合わせることで、AIシステムのスケールアップ/アウトに貢献すると期待される。

製造能力とエコシステム:顧客中心への転換

Intel Foundryの成功には、最先端技術だけでなく、安定した製造能力と、顧客の設計・開発を支援する強固なエコシステムが不可欠である。

グローバルな製造拠点と米国でのリーダーシップ

Intelは、米国(オレゴン、アリゾナ、ニューメキシコ、建設中のオハイオ)、イスラエル、アイルランド、マレーシアなどにグローバルな製造・研究開発拠点を有している。特に、18Aプロセスと関連する研究開発・ウェハ生産はすべて米国内で行われる計画であり、地政学的リスクが高まる中で、米国内で最先端プロセスと先進パッケージングの両方を提供できる唯一の企業としての地位を強調している。アリゾナのFab 52では18Aウェハの最初の処理が成功し、国内製造能力の進捗を示した。Naga Chandrasekaran氏は、過去4年間で約900億ドルを投資し、研究開発競争力強化とグローバルな生産能力拡大を進めてきたと述べた。さらに、既存の工場スペースを活用し、顧客の需要に応じて6~8四半期で生産能力を追加できる体制も整えているとした。

エコシステム強化:Chiplet AllianceとValue Chain Alliance

ファウンドリ事業において、EDAツールベンダー、IPプロバイダー、設計サービスパートナーとの連携は生命線である。Intelは「Intel Foundry Accelerator Alliance」プログラムを拡充し、新たに2つのアライアンスを追加した。

- Intel Foundry Chiplet Alliance: 政府向けアプリケーションや主要商用市場をターゲットに、相互運用可能でセキュアなチップレットソリューションの標準化と普及を目指す。12社以上の企業が参加。

- Value Chain Alliance: 仕様策定からシリコン製造、認定部品供給まで、完全なターンキーソリューションを提供できる3つのパートナー企業で構成される。

これらのアライアンスは、既存のIP、EDA、設計サービス、クラウド、USMAG(米国政府向け)アライアンスと共に、顧客がIntel Foundryの技術を容易に利用できる環境を整備するものである。イベントでは、Synopsys、Cadence、Siemens EDA、PDF SolutionsのCEOが登壇し、Intelとの協力関係の深化と、18Aや14Aへの対応状況、顧客支援へのコミットメントを表明した。特に、設計の難易度に関して、Synopsys CEOは、かつてIntel 10nm世代では競合比2.5~3倍の労力が必要だったが、18Aでは業界標準と同等レベルまで改善されたと述べ、Intel Foundryの使いやすさが劇的に向上したことを証言した。

顧客中心主義へのシフト

Lip-Bu Tan CEOをはじめとする幹部は、ファウンドリ事業成功の鍵は「顧客の信頼を得ること」であり、そのために「顧客中心主義(Customer First Mindset)」への文化変革を進めていることを繰り返し強調した。具体的には、予測可能性(Predictability)、品質(Quality)、速度(Velocity)、手頃な価格(Affordability)の4つの柱に注力し、従来の「Copy Exact」(全工場で同一プロセスを厳密に再現する)方針から「Continuous Improvement」(継続的改善)へと移行し、各工場でのイノベーションを促進する。顧客やパートナーの声に耳を傾け、フィードバックを迅速に反映させる体制を構築している。工場での自動化推進(ロボット検査員「Chip」のデモなど)も、効率化と品質向上の一環として紹介された。

Intel Foundryの挑戦と未来

Intel Foundry Direct Connect 2025で発表された内容は、Intelがファウンドリ事業でリーダーシップを奪還し、「システムファウンドリ」としての地位を確立するための野心的な計画を示している。次世代14Aプロセスの発表、18Aプロセスの3D積層対応への進化、先進パッケージング技術の拡充、そしてエコシステムとの連携強化は、いずれも重要な前進である。

特に、18A-PTによるFoveros Directハイブリッドボンディングの導入は、TSMCの先行技術にキャッチアップし、高性能コンピューティングやAI分野で新たな設計自由度をもたらす可能性を秘めている。また、Amkorとの提携は、顧客にとって重要なサプライチェーンの選択肢拡大につながる。

一方で、これらの計画を予定通り実行し、品質と信頼性を確保していくことが最大の課題となる。新CEO Lip-Bu Tan氏が強調するように、顧客からの信頼獲得なくしてファウンドリ事業の成功はない。TSMCという強力な競合が存在する中で、技術的な優位性を確立し、それを安定的に供給し、かつ顧客が使いやすいエコシステムを提供し続ける必要がある。

今回の発表は、Intel Foundryが正しい方向に進んでいることを示す力強いメッセージであるが、真価が問われるのはこれからである。ロードマップの着実な実行と、顧客中心主義の徹底が、今後のIntel Foundryの成功を左右するだろう。半導体業界の巨人Intelのファウンドリ事業への本格的な挑戦が、業界地図をどう塗り替えていくのか、引き続き注目していく必要がある。

Sources